# ELECTRONIC DEVICES AND ANALOG ELECTRONICS

### **Specially Designed for GATE Examination**

# VOLUME II

### *by* Ram Niwas (IES)

Subscribe "Digcademy" youtube channel for topicwise videos of EDC & AE and join www.digcademy.com for getting free access to study material of EC,EE & IN

# ELECTRONIC DEVICES AND ANALOG ELECTRONICS

## **VOLUME II**

First Edition 2021

# ELECTRONIC DEVICES AND ANALOG ELECTRONICS

## **VOLUME II**

### **RAM NIWAS, IES**

B.E. (NIT, Nagpur), M.E. (DCE, Delhi), Ph.D. (IIT, Delhi)

**First Edition**

2021

### DIGCADEMY

E2/162, SECTOR 11, ROHINI, NEW -110085 Email : digcademy@gmail.com | www.digcademy.com First Edition 2021

#### **COPYRIGHT © AUTHOR**, 2021

All rights reserved. No part of this publication may be reproduced, translated or transmitted in any form (except for review or criticism), without the written permission of the author.

Published by

DIGCADEMY

(A Unit of Daksh Bharat Society)

E2/162, Sector - 11, Rohini, New Delhi-10085

Email : digcademy@gmail.com

## CONTENTS

| HOW  | TO RE  | AD THIS BOOK                                        | xiii  |

|------|--------|-----------------------------------------------------|-------|

| PREF | ACE    |                                                     | XV    |

| GATE | SYLLA  | BUS                                                 | xvii  |

| CHAF | TERWI  | SE ANALYSIS OF GATE QUESTIONS                       | xix   |

|      |        |                                                     |       |

| CHAF | TER 1  | DIODE CIRCUITS                                      | 1-140 |

| 1.1  | Diode  | as Circuit Element                                  | 1     |

|      | 1.1.1  | Equivalent Circuit of an Diode for DC signals       | 1     |

| 1.2  | Clippi | ng Circuits                                         | 2     |

|      | 1.2.1  | One Level Clipper with Shunt Connected Diode        | 2     |

|      | 1.2.2  | One Level Clipper with Series Connected Diode       | 15    |

|      | 1.2.3  | Two Level Clipper with Shunt Connected Diodes       | 25    |

|      | 1.2.4  | Clipping Circuits Using Zener Diodes                | 35    |

| 1.3  | Clamp  | per Circuits                                        | 41    |

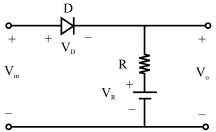

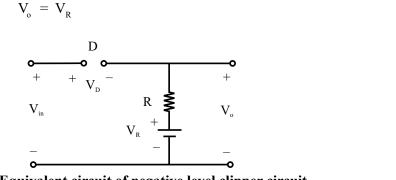

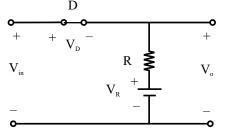

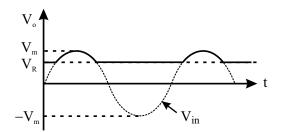

|      | 1.3.1  | Negative Level Clamper Circuits                     | 41    |

|      | 1.3.2  | Positive Level Clamper Circuits                     | 45    |

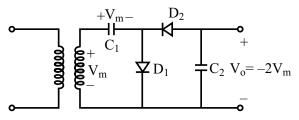

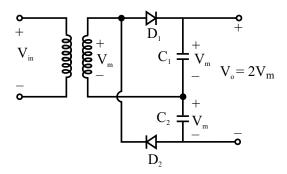

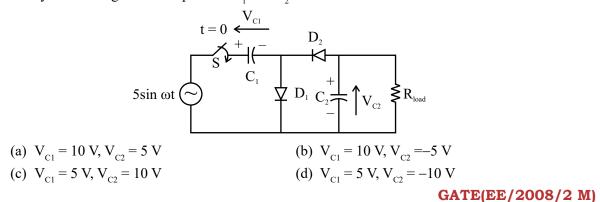

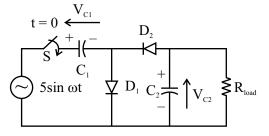

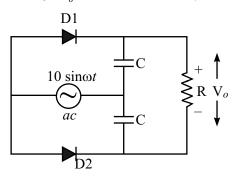

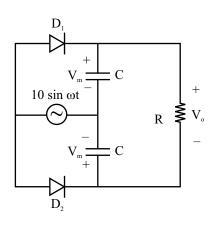

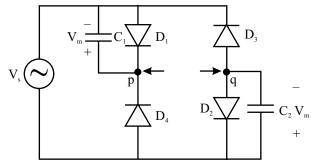

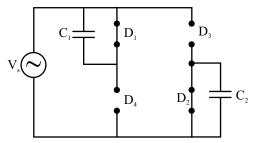

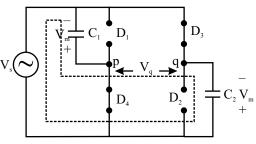

| 1.4  | Voltag | ge Doubler Circuit                                  | 51    |

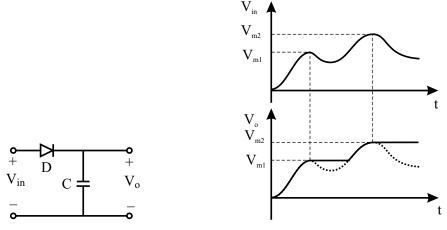

| 1.5  | Peak l | Detector Circuit                                    | 55    |

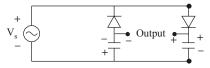

| 1.6  | Rectif | iers                                                | 55    |

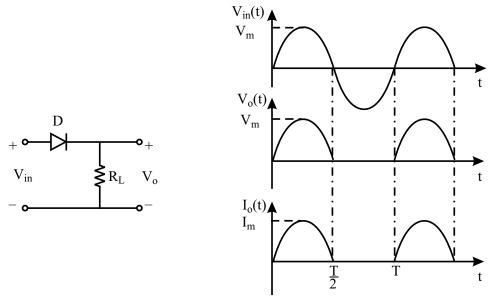

|      | 1.6.1  | Half wave Rectifier                                 | 56    |

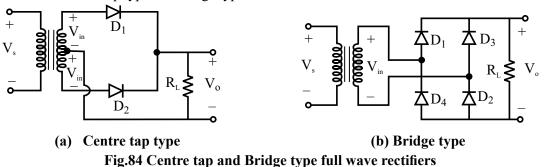

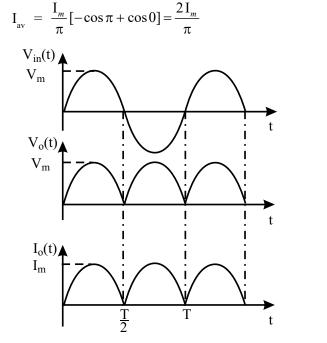

|      | 1.6.2  | Full wave Rectifier                                 | 60    |

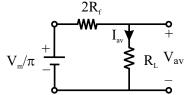

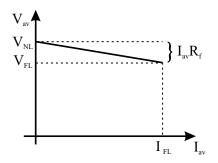

|      | 1.6.3  | Performance Parameters of Rectifiers                | 63    |

|      | 1.6.4  | Comparison of Centre tap and Bridge type rectifiers | 74    |

|      | 1.6.5  | Comparison between half wave and full wave bridge   | 74    |

|      |        | type rectifier                                      |       |

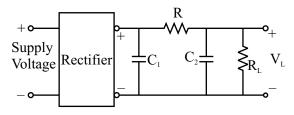

|      | 1.6.6  | Rectifier Filters                                   | 74    |

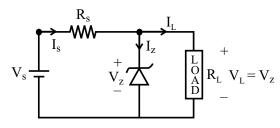

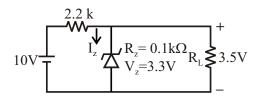

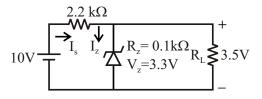

| 1.7  | Zener  | Voltage Regulator                                   | 82    |

| 1.8   | Miscellaneous Diode Circuits         | 92  |

|-------|--------------------------------------|-----|

| GATE  | QUESTIONS                            | 114 |

| Answe | ers & Explanations of GATE Questions | 122 |

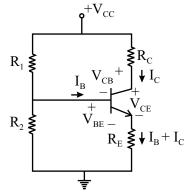

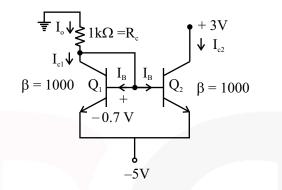

| CHAP | TER 2  | BJT BIASING AND THERMAL STABILIZATION                         | 141-214 |

|------|--------|---------------------------------------------------------------|---------|

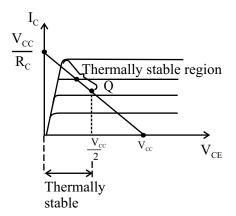

| 2.1  | Conce  | pt of Q-point and load line                                   | 141     |

| 2.2  | Biasin | ng of BJT                                                     | 143     |

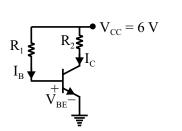

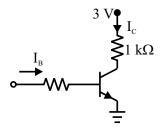

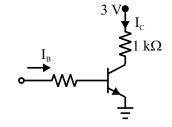

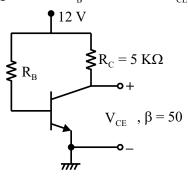

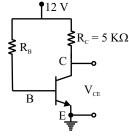

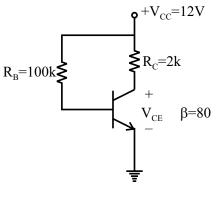

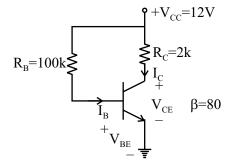

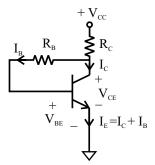

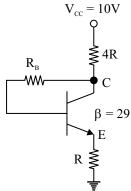

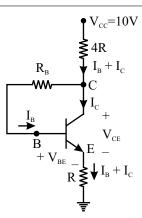

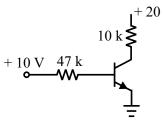

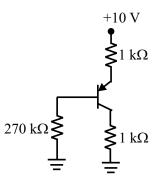

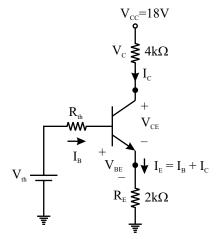

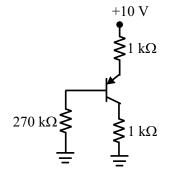

| 2.3  | Fixed  | Bias Circuits of BJT                                          | 144     |

|      | 2.3.1  | Fixed Base Bias Circuit                                       | 144     |

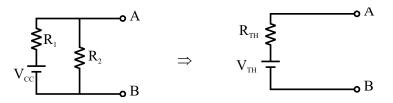

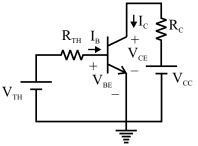

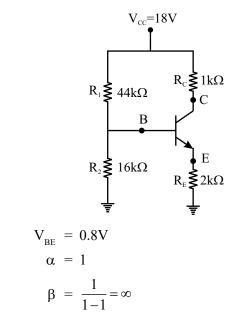

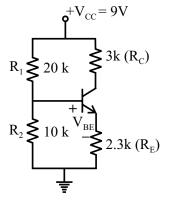

|      | 2.3.2  | Fixed Bias with Potential Divider                             | 153     |

| 2.4  | Self B | ias Circuits                                                  | 157     |

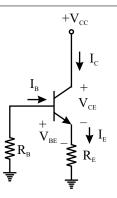

|      | 2.4.1  | Base Bias with Emitter Register                               | 157     |

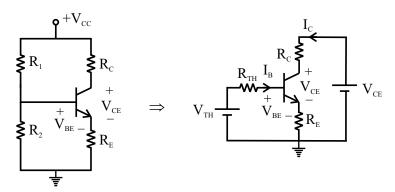

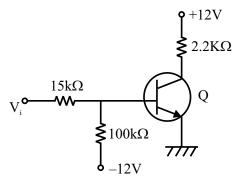

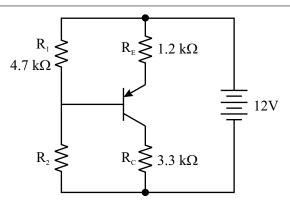

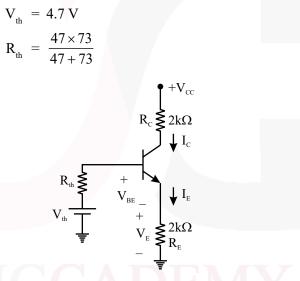

|      | 2.4.2  | Self Bias with Potential Divider                              | 159     |

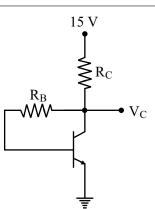

|      | 2.4.3  | Self Bias with Collector Feedback                             | 164     |

| 2.5. | Miscel | llaneous Biasing Circuits                                     | 167     |

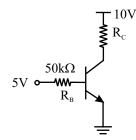

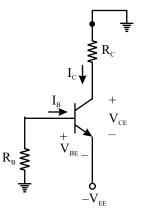

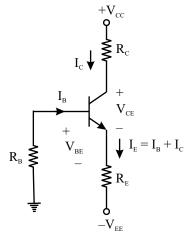

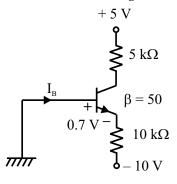

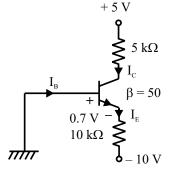

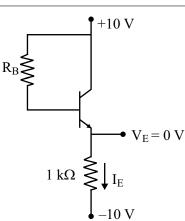

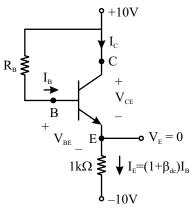

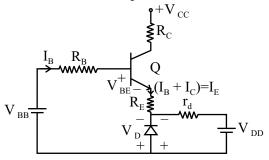

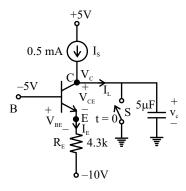

|      | 2.5.1  | Bias Circuit with bias voltage at emitter                     | 167     |

|      | 2.5.2  | Biasing of BJT with Two Power Supplies                        | 167     |

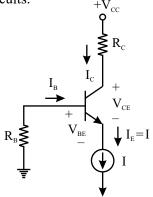

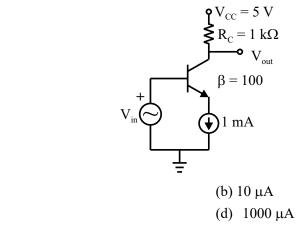

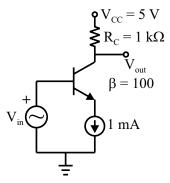

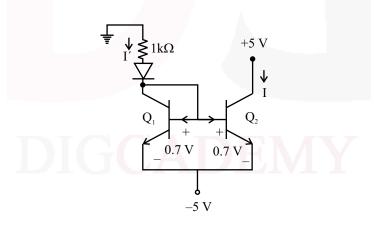

|      | 2.5.3  | Biasing with Current Source                                   | 169     |

|      | 2.5.4  | Biasing of Emitter Follower or Common Collector Configuration | 170     |

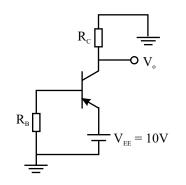

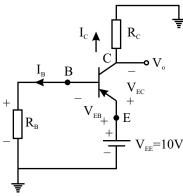

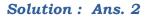

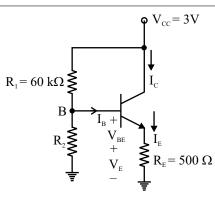

|      | 2.5.5  | Biasing of PNP transistors                                    | 173     |

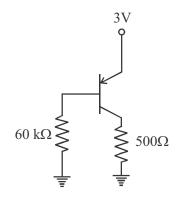

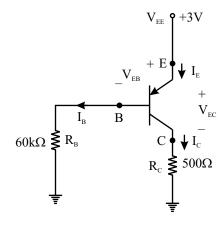

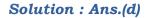

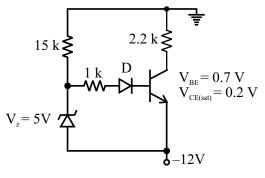

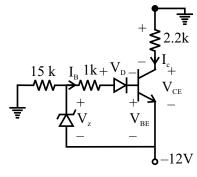

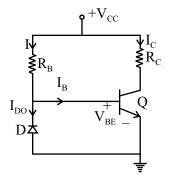

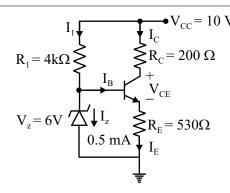

|      | 2.5.6  | BJT Biasing with Zener Diode                                  | 176     |

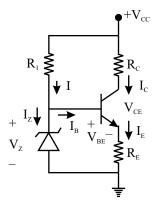

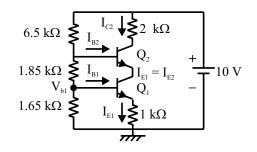

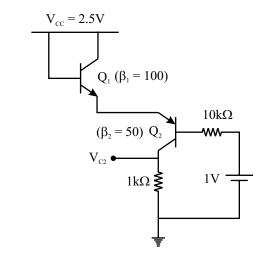

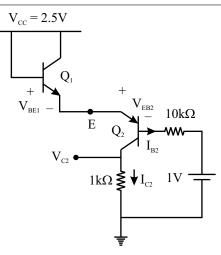

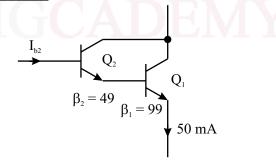

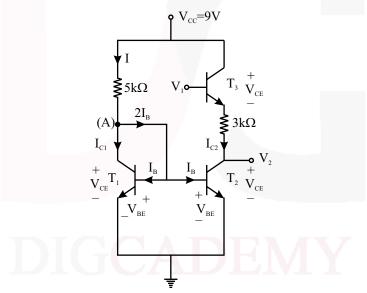

|      | 2.5.7. | Examples on Biasing of Composite Circuits                     | 179     |

| 2.6  | Bias S | Stability and Stability Factors                               | 181     |

|      | 2.6.1  | Stability factors of potential divider self bias circuit      | 182     |

| 2.7  | Bias C | Compensation                                                  | 185     |

|      | 2.7.1  | Bias Compensation for $V_{_{BE}}$                             | 185     |

|      | 2.7.2  | Bias Compensation for I <sub>co</sub>                         | 186     |

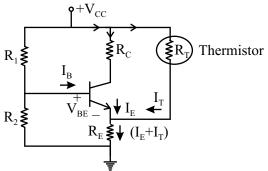

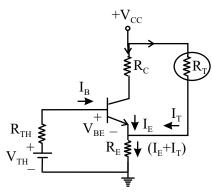

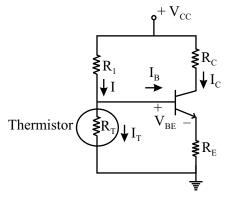

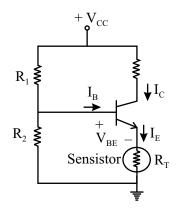

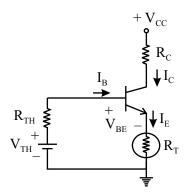

|      | 2.7.3  | Bias Compensation using Thermistor                            | 187     |

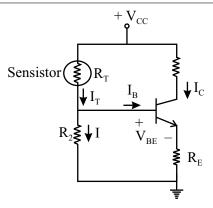

|      | 2.7.4  | Bias Compensation using Sensistor                             | 188     |

| 2.8   | Thermal Runaway and Thermal Stability | 190 |

|-------|---------------------------------------|-----|

| GATE  | PRACTICE QUESTIONS                    | 194 |

| Answe | ers & Explanations of GATE Questions  | 200 |

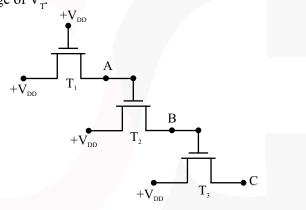

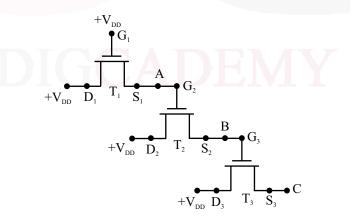

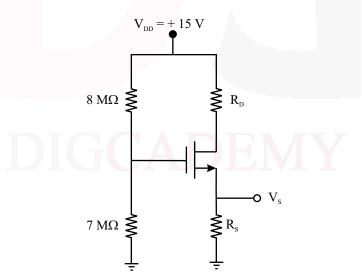

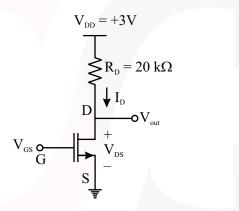

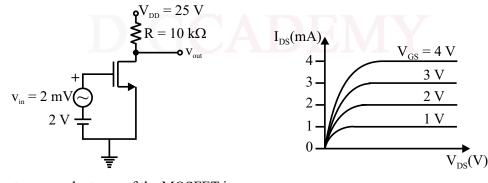

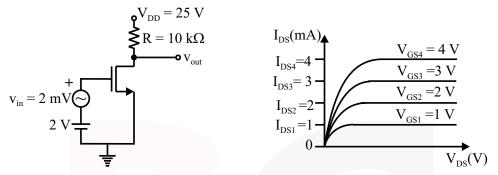

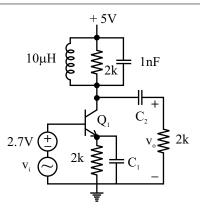

| CHA | APTER 3 MOSFET AND JFET BIASING                           | 215-278 |

|-----|-----------------------------------------------------------|---------|

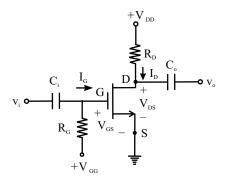

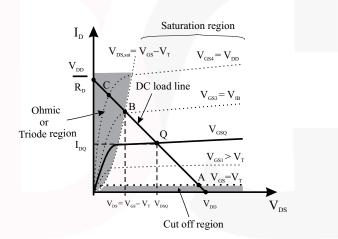

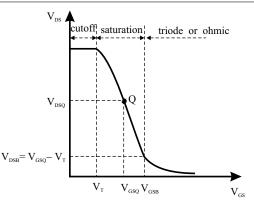

| 3.1 | Concept of Q-point and load line                          | 215     |

| 3.3 | Biasing Circuits of MOSFET                                | 218     |

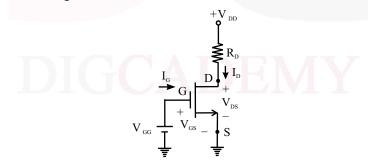

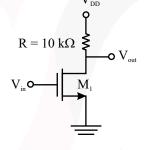

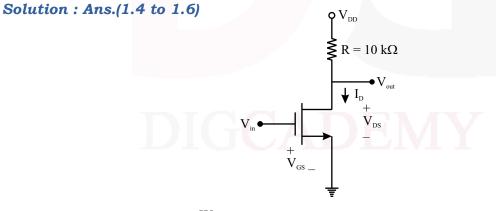

|     | 3.3.1 Biasing of N-MOSFET By Fixing Voltage $V_{GS}$      | 218     |

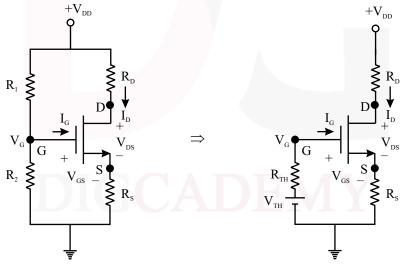

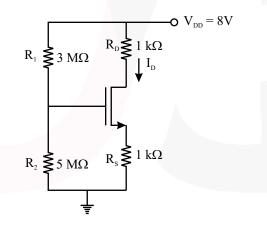

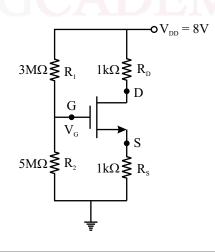

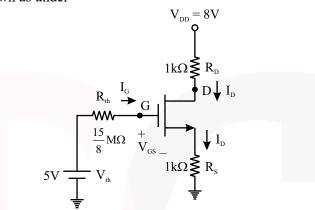

|     | 3.3.2 Biasing of N-MOSFET with Potential Divider          | 220     |

|     | 3.3.3 Biasing of N-MOSFET with Feedback Configuration     | 223     |

|     | 3.3.4 Biasing of N-MOSFET with Two Power Supplies         | 225     |

|     | 3.3.5 Biasing of N-MOSFET with a Constant Current Source  | 225     |

|     | 3.3.6 Biasing of P-MOSFET                                 | 226     |

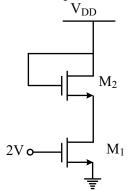

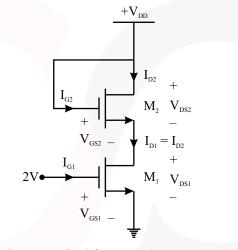

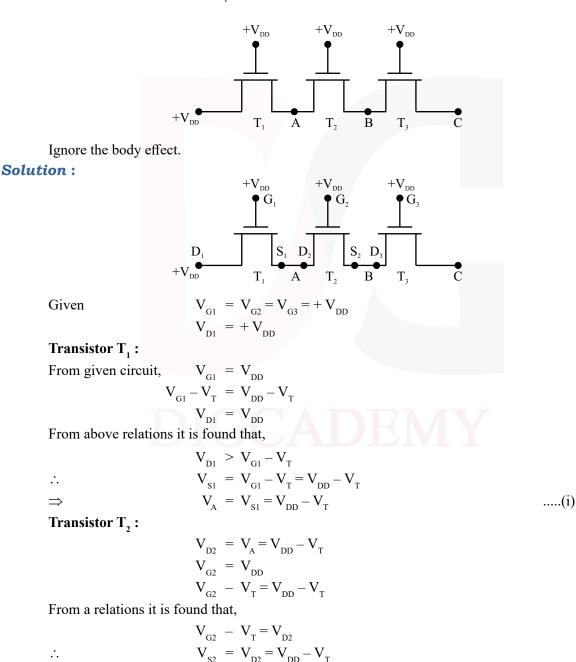

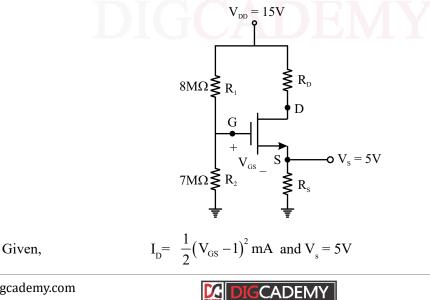

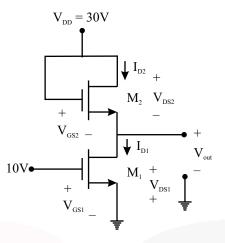

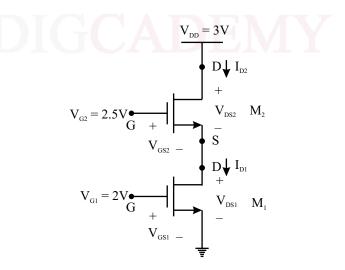

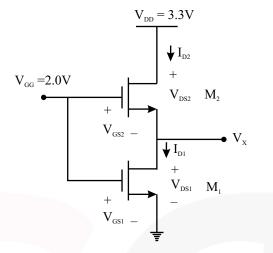

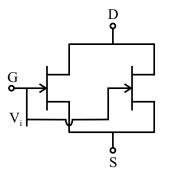

|     | 3.3.7 Examples on Biasing of Combination of MOSFETs       | 229     |

| 3.4 | Biasing Circuits of JFET                                  | 234     |

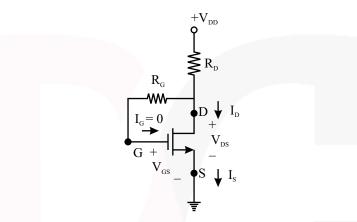

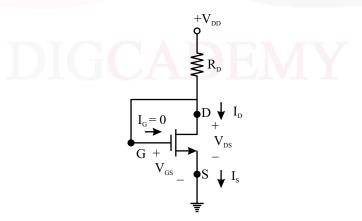

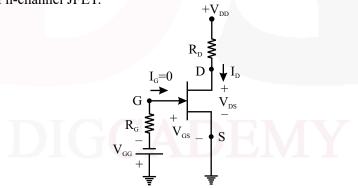

|     | 3.4.1 Fixed Bias Configuration of JFET                    | 234     |

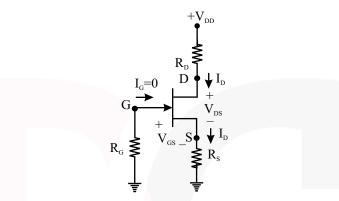

|     | 3.4.2 Self Bias Configuration of JFET                     | 235     |

|     | 3.4.3 Potential Divider Bias Configuration of JFET        | 237     |

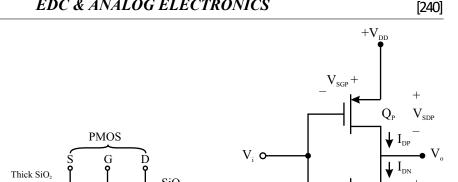

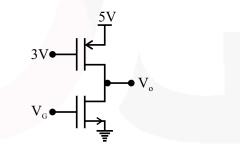

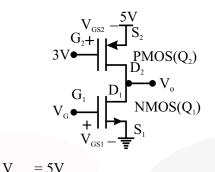

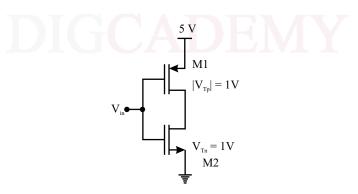

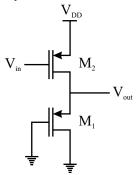

| 3.5 | Complementary MOS (CMOS) Logic Inverter                   | 239     |

|     | 3.5.1 Construction of CMOS                                | 239     |

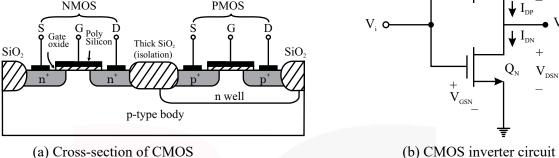

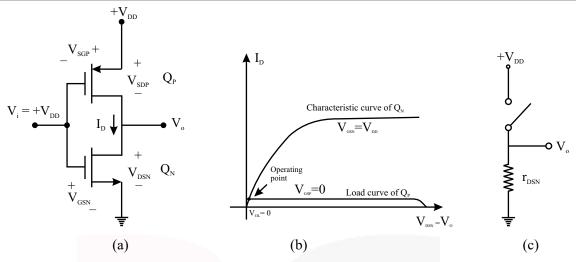

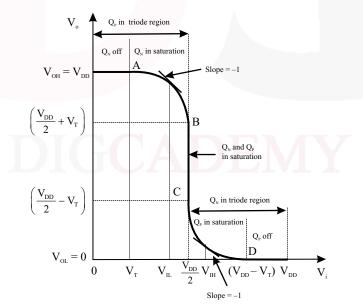

|     | 3.5.2 Circuit Operation of CMOS Inverter                  | 240     |

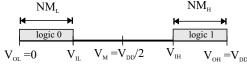

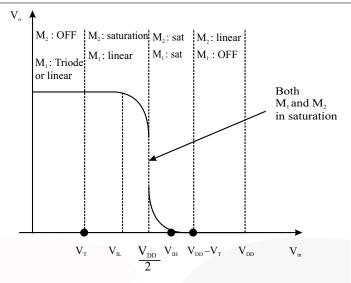

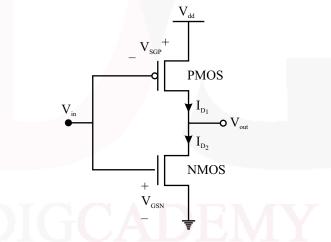

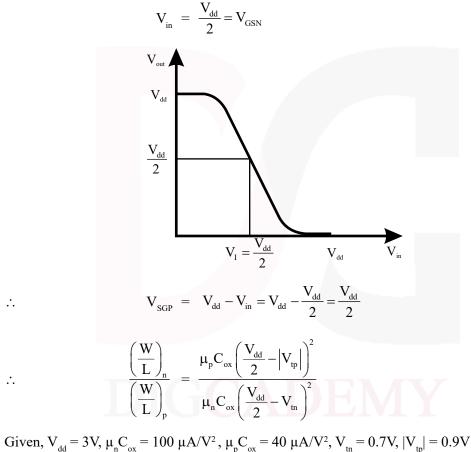

|     | 3.5.3 Voltage Transfer Characteristics of CMOS            | 242     |

|     | 3.5.4 Noise Margins of CMOS                               | 246     |

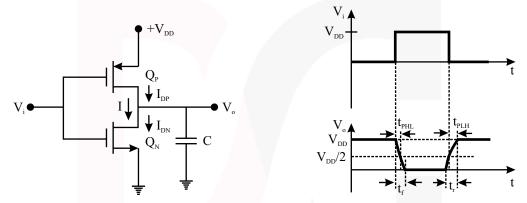

|     | 3.5.5 Dynamic Operation of CMOS                           | 249     |

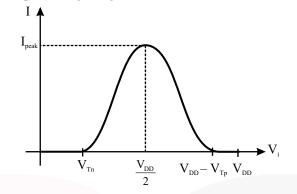

|     | 3.5.6 Current flow and power dissipation in CMOS Inverter | 251     |

|     | 3.5.7 Advantages of CMOS inverter                         | 251     |

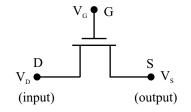

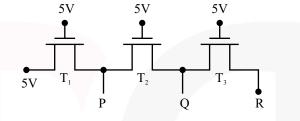

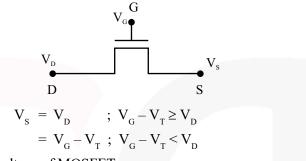

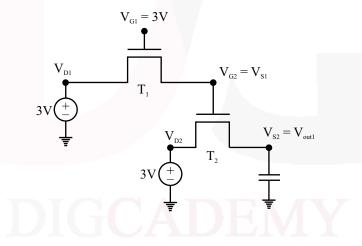

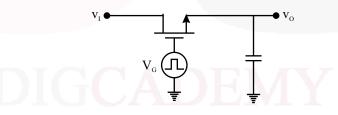

| 3.6 | NMOS Pass Transistor                                      | 255     |

Answers & Explanations of GATE Questions 265

GATE QUESTIONS 259

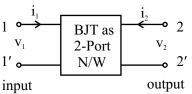

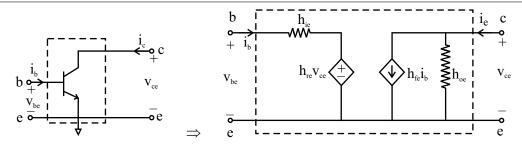

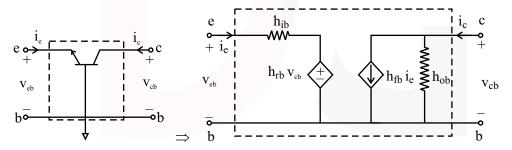

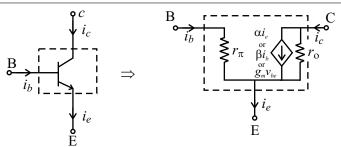

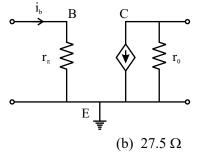

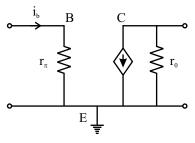

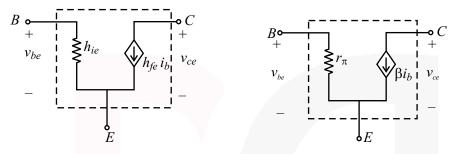

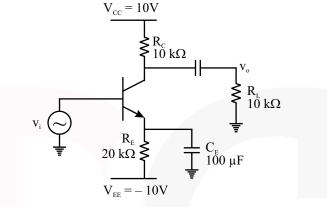

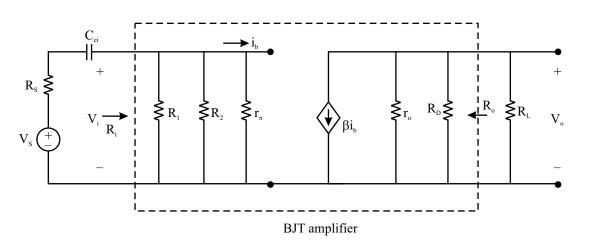

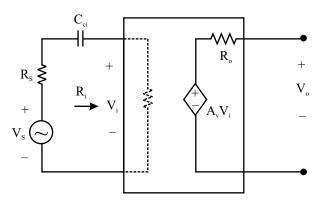

| CHAP | TER 4                 | SMALL SIGNAL ANALYSIS OF BJT                                          | 279-364 |

|------|-----------------------|-----------------------------------------------------------------------|---------|

| 4.1  | Introd                | luction                                                               | 279     |

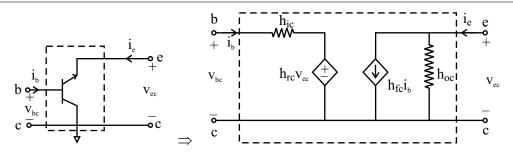

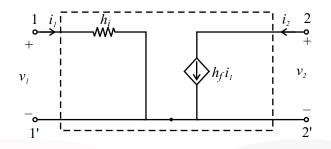

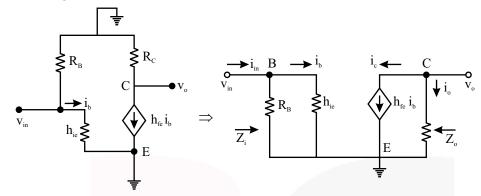

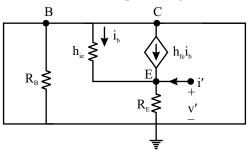

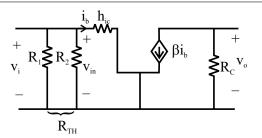

| 4.2  | h-para                | ameter model of BJT                                                   | 279     |

|      | 4.2.1                 | h-parameter Model of Common Emitter Configuration                     | 280     |

|      | 4.2.2                 | h-parameter Model of Common Base Configuration                        | 281     |

|      | 4.2.3                 | h-parameter Model of Common Collector Configuration                   | 281     |

|      | 4.2.4                 | Relation between h-parameters                                         | 282     |

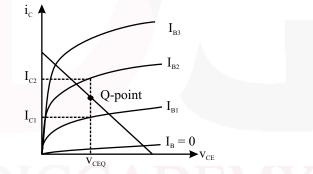

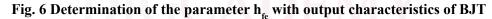

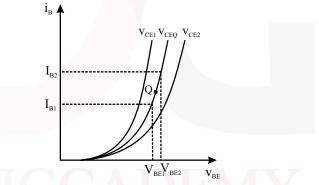

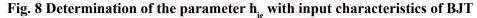

|      | 4.2.5                 | Graphical Method of measurement of h-parameters                       | 282     |

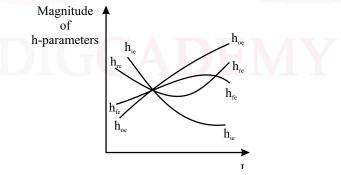

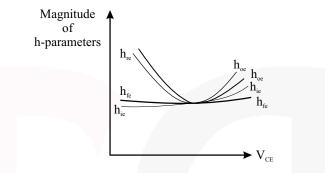

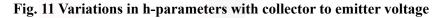

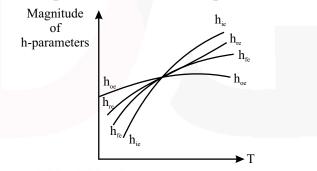

|      | 4.2.6                 | Variations of h-parameter of BJT                                      | 285     |

|      | 4.2.7                 | Values of <i>h</i> -parameters of various configuration               | 286     |

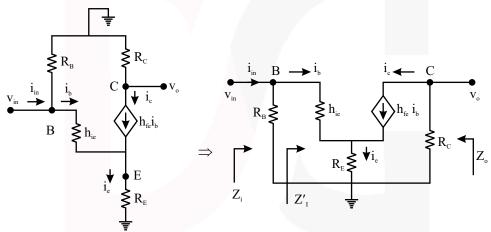

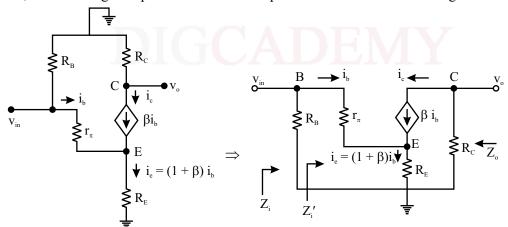

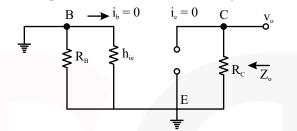

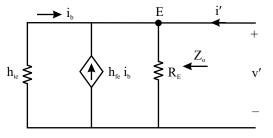

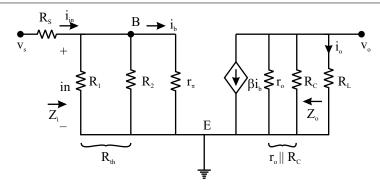

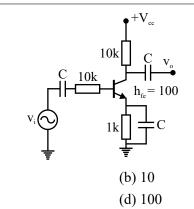

| 4.3  | Analys                | sis of an amplifier with h-parameters model                           | 287     |

| 4.4  | Appro                 | ximate h-parameter model and Amplifier Analysis                       | 291     |

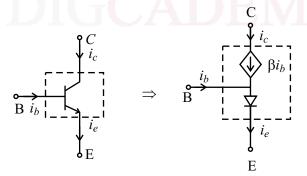

| 4.5  | Diode                 | model of BJT                                                          | 293     |

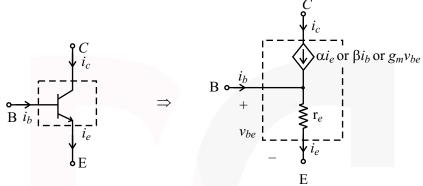

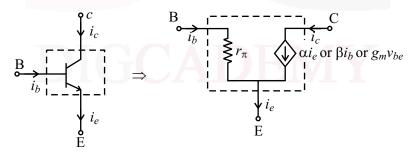

| 4.6  | $r_e^{}, r_{\pi}^{},$ | , $\boldsymbol{r}_o$ and $\boldsymbol{g}_m$ parameters of BJT         | 293     |

|      | 4.6.1                 | $r_e$ -model or T-model of BJT                                        | 296     |

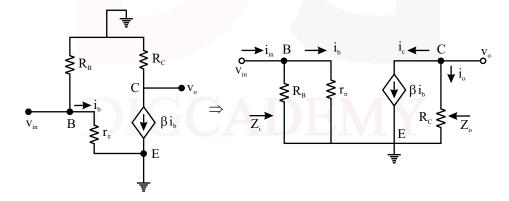

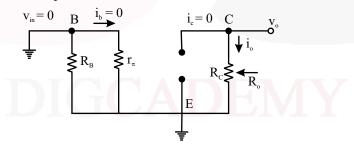

|      | 4.6.2                 | $\pi$ -model of BJT                                                   | 296     |

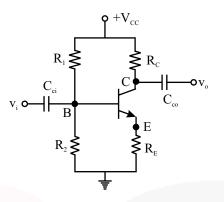

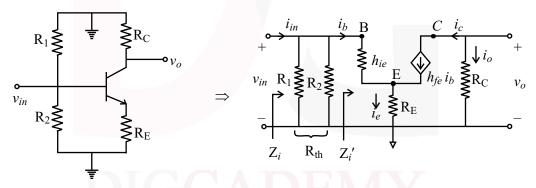

| 4.7  | Compa                 | rison of approximate <i>h</i> -parameter model and $\pi$ model of BJT | 299     |

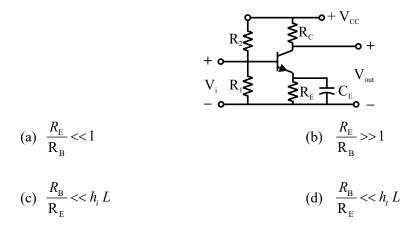

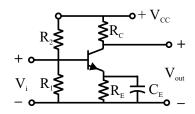

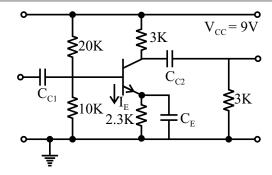

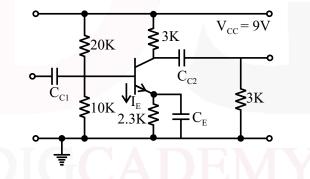

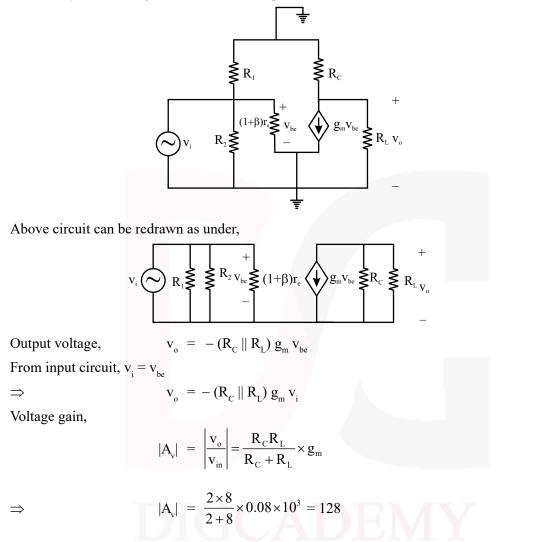

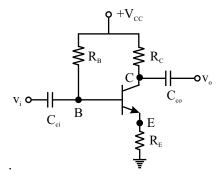

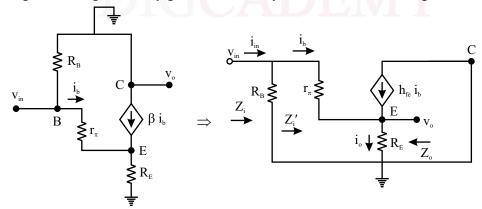

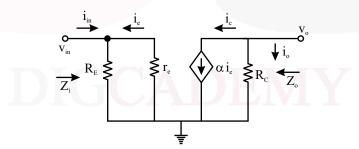

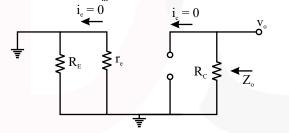

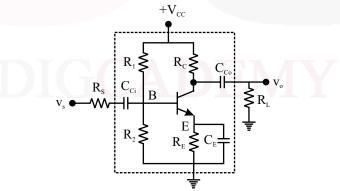

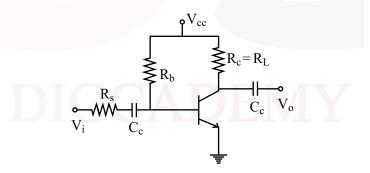

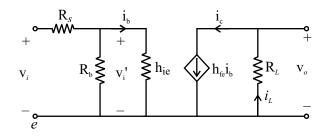

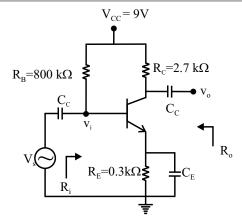

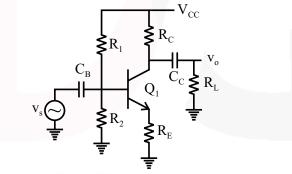

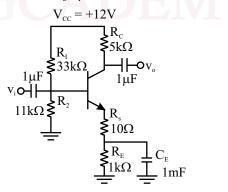

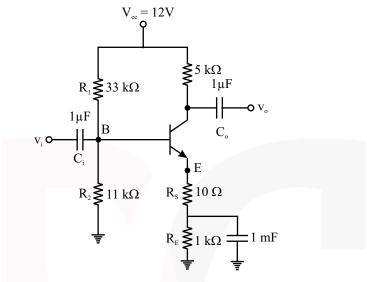

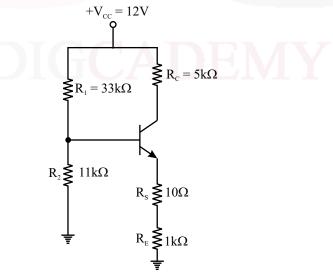

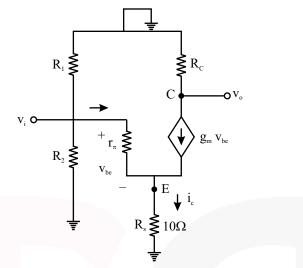

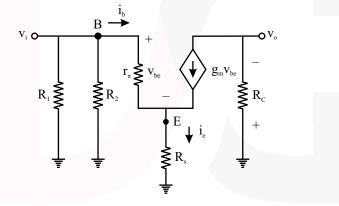

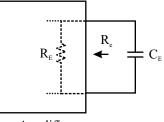

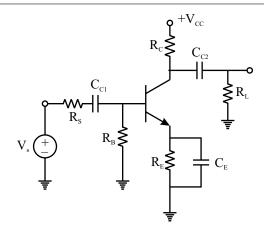

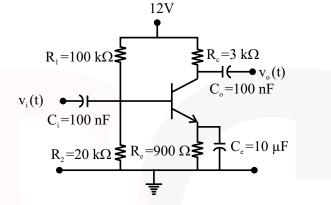

| 4.8  | Small                 | Signal Analysis of Potential Divider Biased CE Amplifier              | 299     |

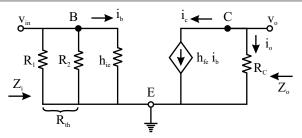

|      | 4.8.1                 | Small Signal Analysis of Potential Divider Biased Without CE          | 299     |

|      |                       | Amplifier Emitter Bypass Capacitor                                    |         |

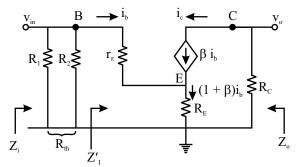

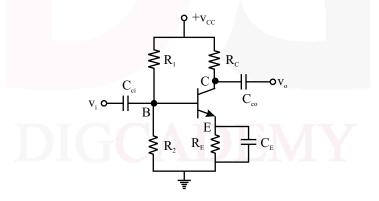

|      | 4.8.2                 | Small Signal Analysis of Potential Divider Biased CE Amplifier        | 304     |

|      |                       | With Emitter Bypass Capacitor                                         |         |

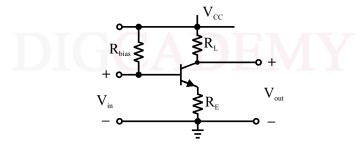

| 4.9  | Small                 | Signal Analysis of Base Bias Amplifier                                | 317     |

|      | 4.9.1                 | Small Signal Analysis of Base Bias Amplifier with Emitter Resistant   | nce 317 |

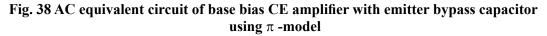

|      | 4.9.2                 | Analysis of Base Bias CE Amplifier with Emitter Bypass Capacitor      | 320     |

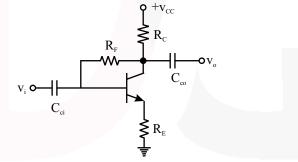

| 4.10 | Small                 | Signal Analysis of Collector Feedback CE Amplifier                    | 325     |

|      | 4.10.1                | Small Signal Analysis of Collector Feedback CE Amplifier              | 325     |

|      |                       | With Emitter Resistance                                               |         |

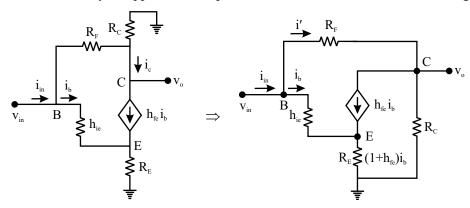

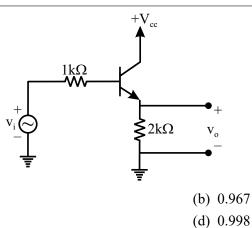

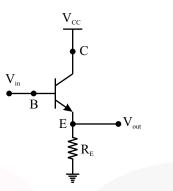

| 4.11 | Small                 | Signal Analysis of Emitter Follower Amplifier                         | 327     |

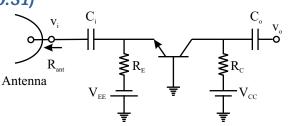

| 4.12  | Small   | Signal Analysis of Common Base Amplifier Using $\pi$ -Model    | 332     |

|-------|---------|----------------------------------------------------------------|---------|

| 4.13  | Effect  | of Source Resistance and Load Resistance                       | 334     |

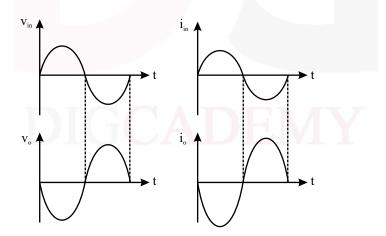

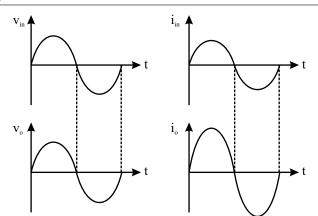

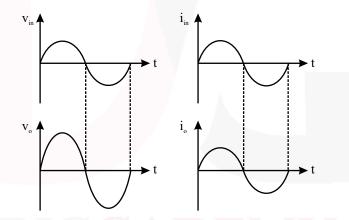

| 4.14. | Phaso   | r Relations of Input and Output Signals of BJT Amplifiers      | 337     |

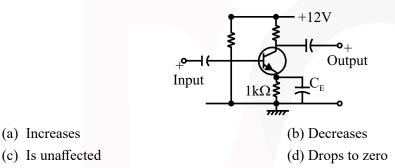

| 4.15. | Effects | s Emitter Resistance and Emitter By Pass Capacitor             | 338     |

| 4.16  | Comp    | arison of Parameters of CE, CC and CB amplifier                | 339     |

| 4.17  | Power   | gain, Voltage Gain and Current Gain of the amplifiers in dB    | 339     |

| GATE  | QUES'   | TIONS                                                          | 342     |

| Answ  | ers & E | xplanations of GATE Questions                                  | 348     |

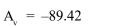

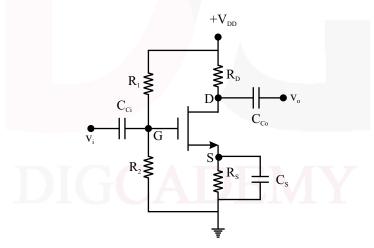

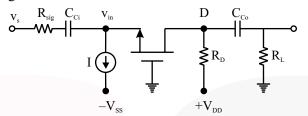

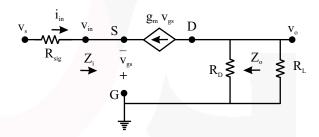

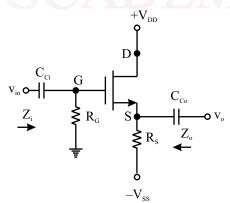

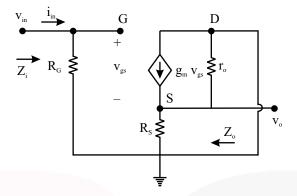

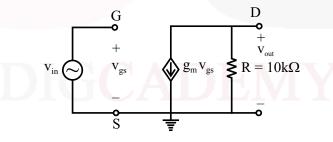

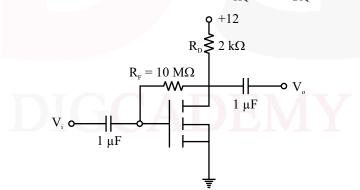

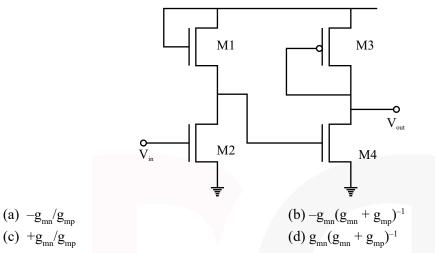

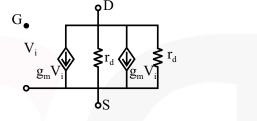

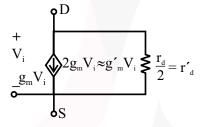

| CHAP  | TER 5   | SMALL SIGNAL ANALYSIS OF MOSFETs                               | 365-392 |

| 5.1   | Introd  | uction                                                         | 365     |

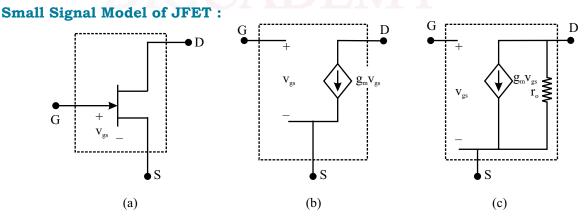

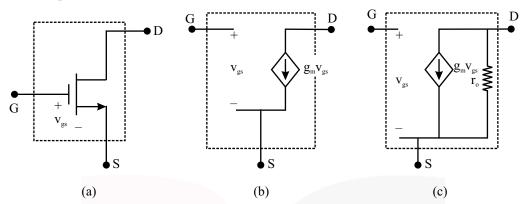

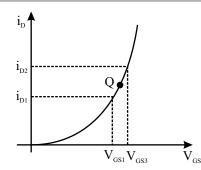

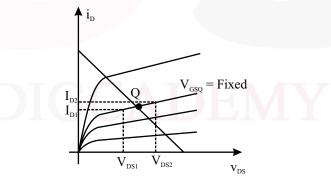

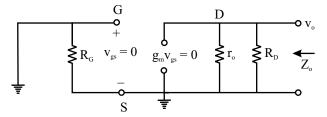

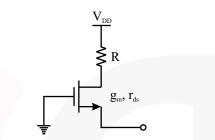

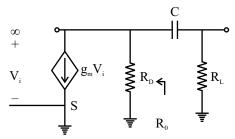

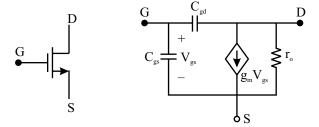

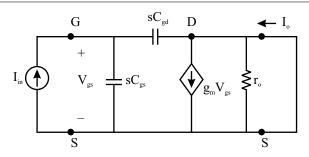

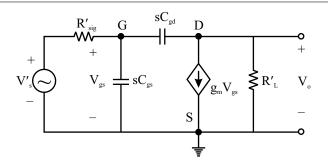

| 5.2   | Small   | Signal Model of FETs                                           | 366     |

| 5.3   | Graph   | ical Method of Determination of Transconductance ( $g_m$ ) and | 369     |

|       | Drain   | Resistance (r <sub>o</sub> )                                   |         |

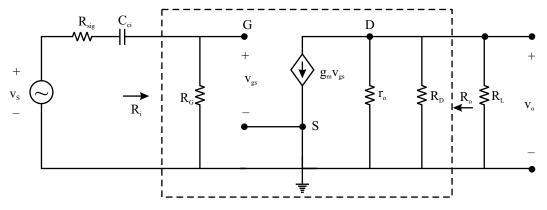

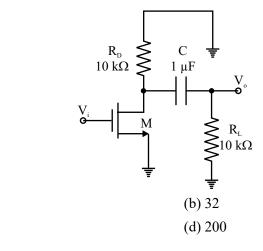

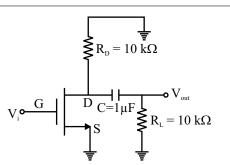

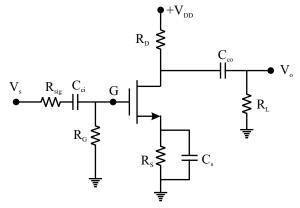

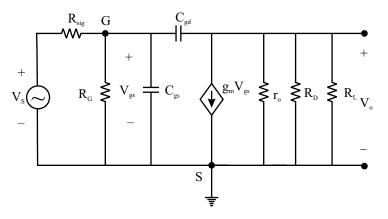

| 5.4   | Small   | Signal Analysis of MOSFET Amplifiers                           | 371     |

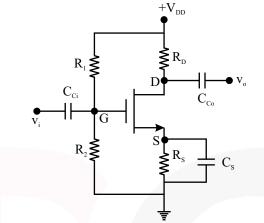

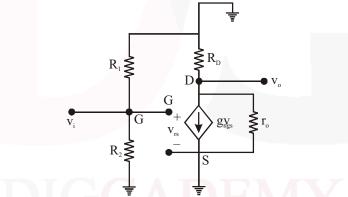

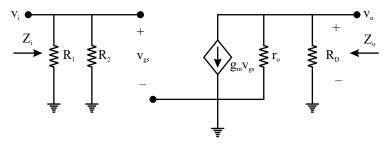

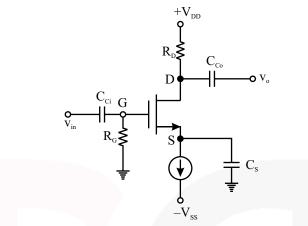

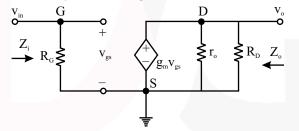

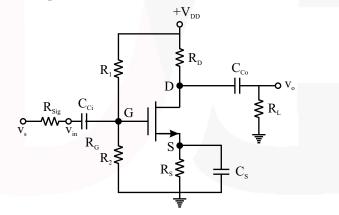

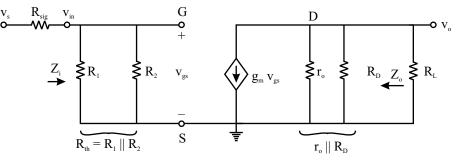

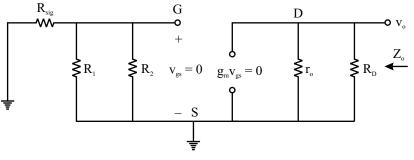

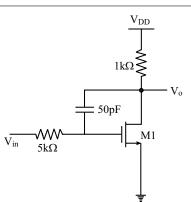

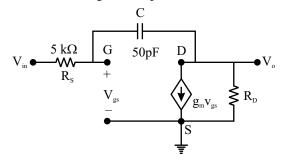

|       | 5.4.1   | Analysis of Potential Divider Bias Common Source n-MOSFET      | 371     |

|       |         | Amplifier                                                      |         |

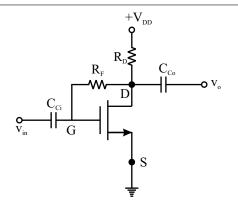

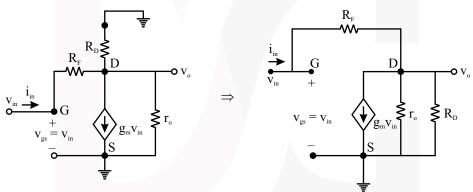

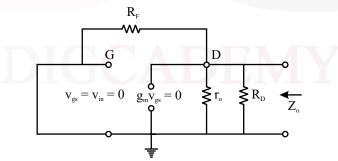

|       | 5.4.2   | Analysis of Common Source Drain Feedback n-MOSFET Amplifie     | r 372   |

|       | 5.4.3   | Analysis of Common Source Fixed Bias n-MOSFET Amplifier        | 375     |

|       | 5.4.4   | Effect of Source and Load Resistances on Parameters of         | 376     |

|       |         | MOSFET Amplifiers                                              |         |

|       | 5.4.5   | Common Gate n-MOSFET Amplifier                                 | 378     |

|       | 5.4.6   | Common-Drain or Source-Follower Amplifier                      | 379     |

| GATE  | QUES'   | TIONS                                                          | 384     |

| Answe | ers & E | xplanations of GATE Questions                                  | 387     |

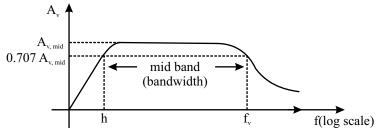

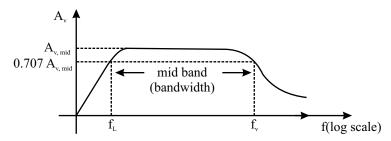

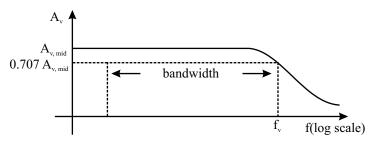

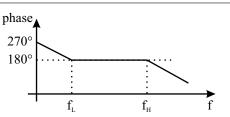

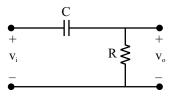

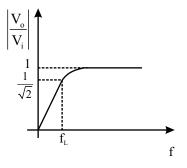

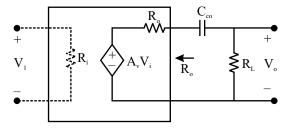

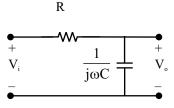

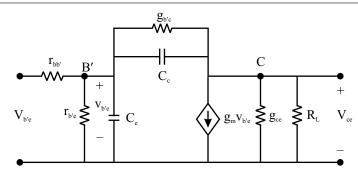

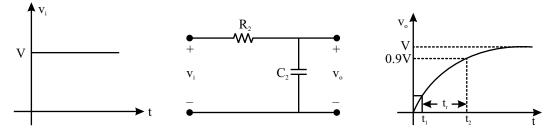

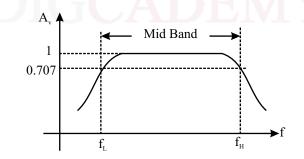

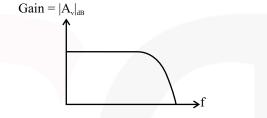

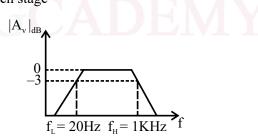

| СНАР  | TER 6   | FREQUENCY RESPONSE                                             | 393-446 |

| 6.1   | Introd  | uction                                                         | 393     |

| 6.2   | Frequ   | ency Response of High Pass RC Circuit                          | 396     |

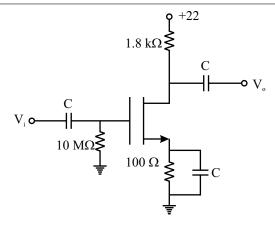

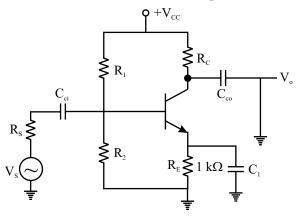

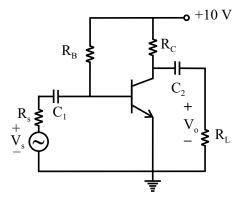

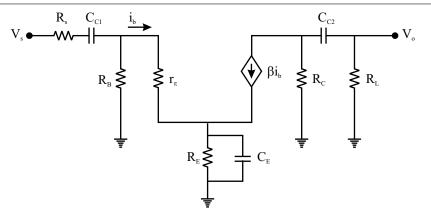

| 6.3   | Low F   | requency Response of BJT Amplifier                             | 397     |

|       |         |                                                                |         |

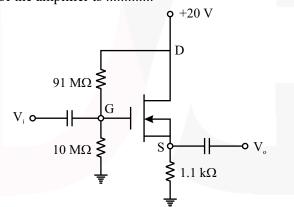

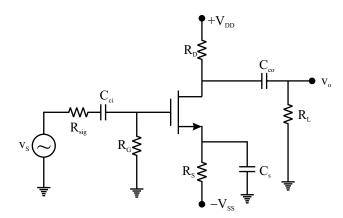

| 6.4   | Low F   | requency Response of MOSFET Amplifier                      | 403     |

|-------|---------|------------------------------------------------------------|---------|

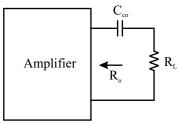

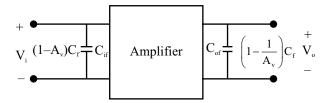

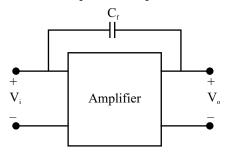

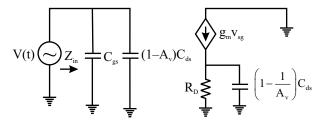

| 6.5   | Miller  | Effect                                                     | 406     |

|       | 6.5.1   | Miller Effect Capacitances                                 | 408     |

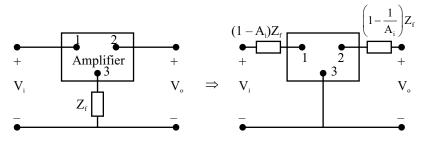

|       | 6.5.2   | Dual of Miller Theorem :                                   | 410     |

| 6.6   | Frequ   | ency Response of Low Pass RC Circuit                       | 410     |

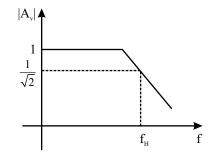

| 6.7   | High    | Frequency Response of BJT Amplifier                        | 411     |

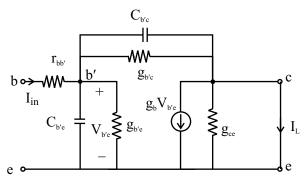

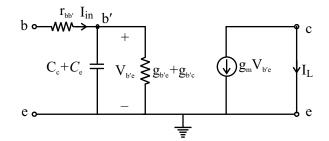

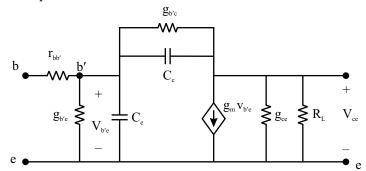

|       | 6.7.1   | Hybrid π-model of BJT                                      | 411     |

|       | 6.7.2   | Conductances and Resistances of Hybrid $\pi$ -model of BJT | 412     |

|       | 6.7.3   | Capacitances of BJT in Hybrid $\pi$ -Model                 | 413     |

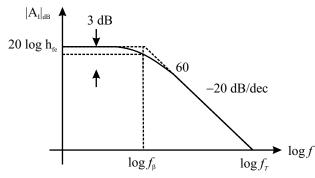

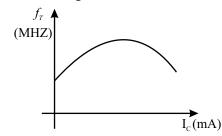

|       | 6.7.4   | Short Circuit Current Gain of BJT Amplifier                | 416     |

|       | 6.7.5   | Frequency Response of BJT Amplifier with Resistive Load    | 422     |

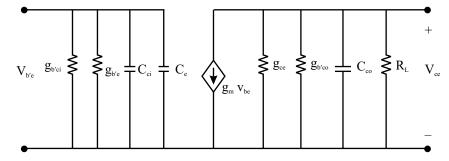

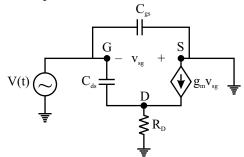

| 6.8   | High    | Frequency Response of MOSFET Amplifiers                    | 425     |

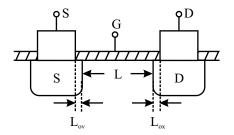

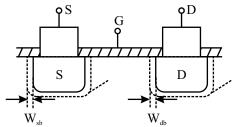

|       | 6.8.1   | MOSFET Internal Capacitances                               | 425     |

|       | 6.8.2   | High Frequency Model of MOSFET                             | 427     |

|       | 6.8.3   | Short circuit current gain of MOSFET                       | 427     |

|       | 6.8.4   | High Frequency Response of Common Source Amplifier         | 429     |

| 6.9   | Step I  | Response of An Amplifier                                   | 433     |

| 6.10. | Noise   |                                                            | 435     |

| GATE  | QUES    | TIONS                                                      | 438     |

| Answ  | ers & E | Explanations of GATE Questions                             | 441     |

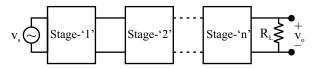

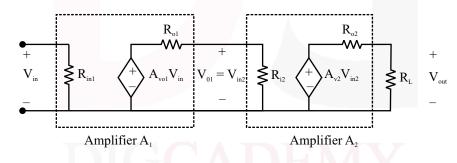

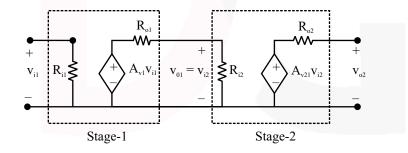

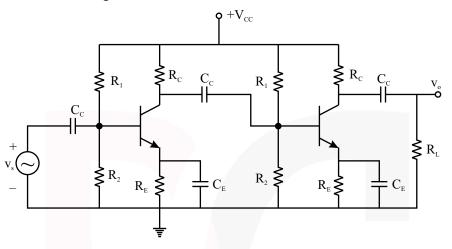

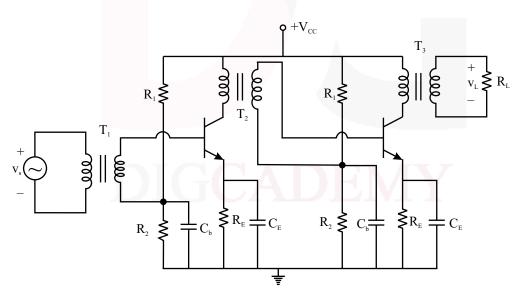

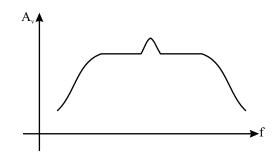

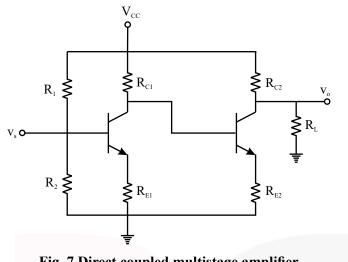

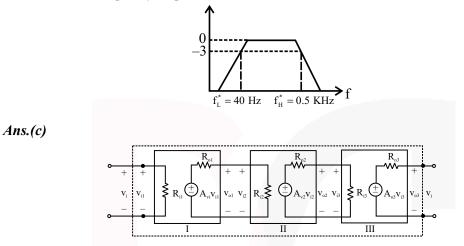

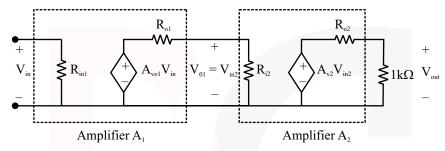

| CHAP  | TER 7   | MULTISTAGE AMPLIFIERS                                      | 447-462 |

| 7.1   | Introd  | luction                                                    | 447     |

| 7.2   | Voltag  | ge, Current and Power Gains of Multistage Amplifiers       | 447     |

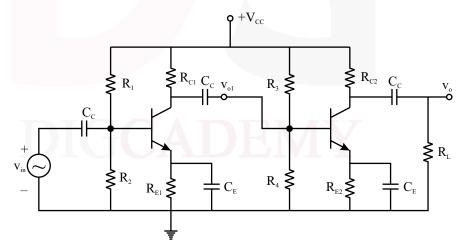

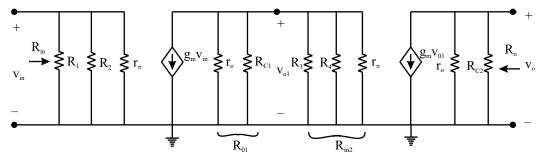

| 7.3   | RC Co   | oupled Multistage Amplifier                                | 450     |

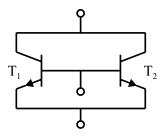

| 7.4   | Trans   | former Coupled Multistage Amplifier                        | 451     |

| 7.5   | Direct  | t Coupled Amplifier                                        | 452     |

| 7.6   | Effect  | s of Multistaging on Frequency Response                    | 454     |

| GATE  | QUES    | TIONS                                                      | 457     |

| Answ  | ers & E | Explanations of GATE Questions                             | 460     |

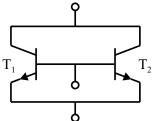

| CHAP  | TER 8 COMPOUND CONFIGURATIONS        | 463-502 |

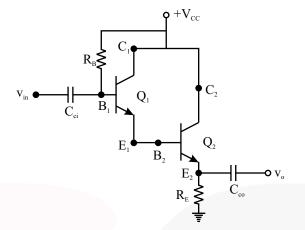

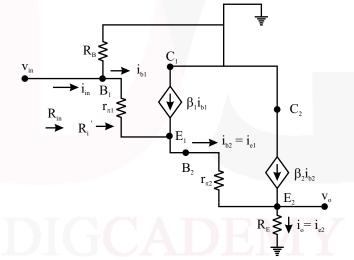

|-------|--------------------------------------|---------|

| 8.1   | Introduction                         | 463     |

| 8.2   | Cascade Connection                   | 463     |

| 8.3   | Darlington Pair                      | 464     |

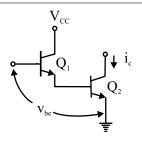

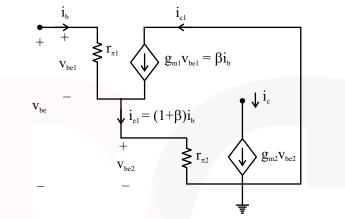

| 8.4   | Cascode Connection                   | 469     |

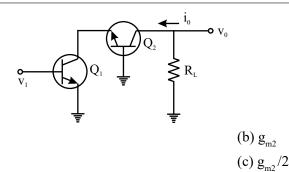

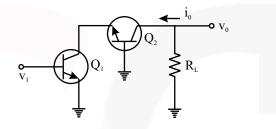

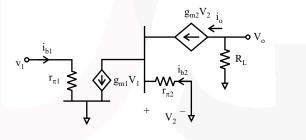

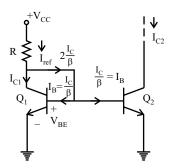

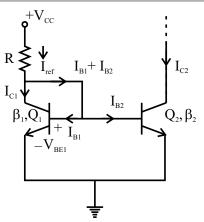

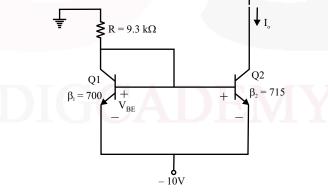

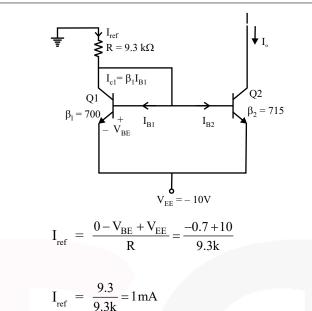

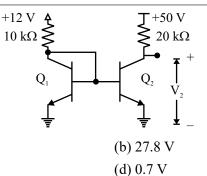

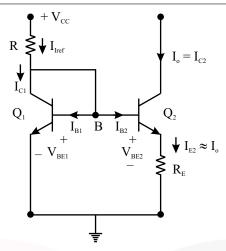

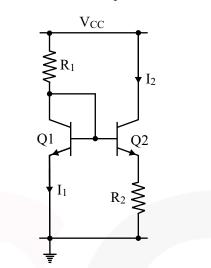

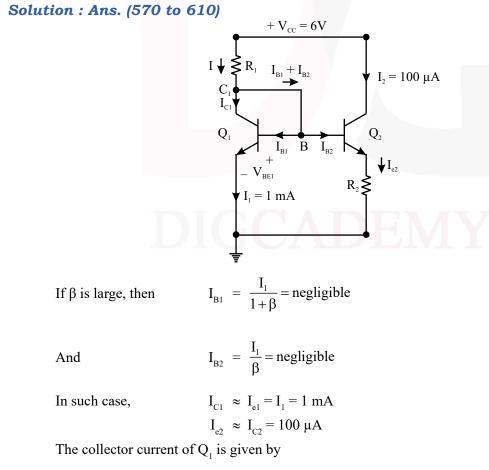

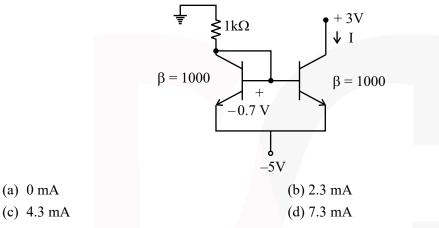

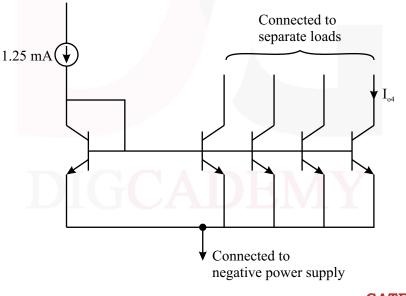

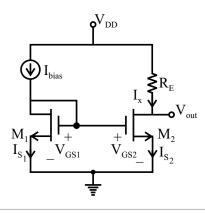

| 8.5   | Current Mirror                       | 472     |

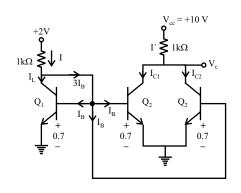

|       | 8.5.1 Current Mirror Using BJT       | 472     |

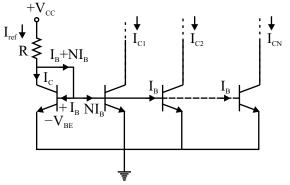

|       | 8.5.2 Current Repeater               | 477     |

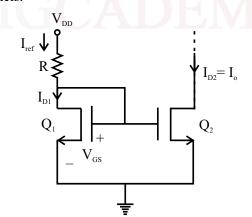

|       | 8.5.3 Current Mirror Using MOSFETs   | 479     |

|       | 8.5.4 Wilder Current Source          | 480     |

| GATE  | QUESTIONS                            | 484     |

| Answe | ers & Explanations of GATE Questions | 490     |

## **HOW TO READ THIS BOOK**

This book has been designed to meet the requirement of all Electrical, Electronics and Instrumentation Engineers. It is has been written in simple and lucid language so that students from all backgrounds, having little knowledge of English, can understand. It is designed to develop facts and concepts for competitive examinations in India like GATE, IES, PSUs and IAS examinations. The book can be referred for University Syllabus across different countries in the world. Every chapter is followed and prepared after in depth analysis of previous year questions which appeared in these competitive examinations. The focus is mainly on developing concepts along with facts. Each chapter has been followed by previous years fully solved questions of GATE of Electronics, Electrical and Instrumentation Engineering. These questions are helpful for university examination also.

#### For students studying in B.E./B.Tech

This book would help students studying in B.Tech to prepare for their university examination. In parallel book is equipped to prepare B.Tech students for competitive examinations like GATE and ESE. However, main focus of students of B.Tech should be to develop concepts and then practice question of GATE.

#### For students preparing for GATE

The theory of this book has been prepared to develop theoretical concepts for those students who are preparing for GATE. Such students should focus on theoretical concepts followed by practicing previous year GATE questions which are given at the end of each chapter along with full solutions. Students first try to solve the question themselves and the refer the solution.

#### For students preparing for ESE Preliminary

The theory of this book has been prepared for students preparing for ESE both Electrical and Electronics Preliminary and Mains Examinations and IAS Electrical mains examination. However, students preparing for ESE Pre examination should note down factual information and formulas in their notebook in form of brief notes. It helps in quick revision just before the Pre examination. Each chapter has been provided with fully solved questions of ESE Pre for both EE and EC. Students should practice these questions in time bound manner with one question in one minute. It would help to build speed and accuracy. Solutions should be referred only to clarify doubt if any.

#### For students preparing for ESE Mains and IAS Mains

The students preparing for ESE Mains of EE and EC or IAS Electrical mains should practice questions from all these examination so that they have enough practice questions. However, solutions of these question will be provided in next edition of this book. Such students should not wast much time on reading theory in whole they should relevant portion which are important for mains examination as they have already studied the whole theory while preparing for preliminary stage.

### **PREFACE TO FIRST EDITION**

### Chapter 1

Chapter 1 introduces different circuits of diodes. It presents clipping circuits, clamping circuits, peak detectors, rectifiers and zener voltage regulator. This chapter is very important for almost all the competitive examinations including GATE & ESE for students of Electronics, Electrical as well as Instrumentation Engineering. There are questions from this chapter almost every year in GATE and Engineering services Examinations.

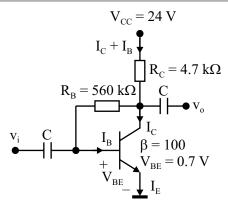

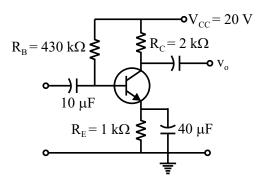

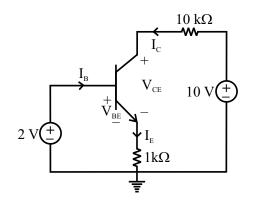

### Chapter 2

Chapter 2 presents different biasing circuits of BJT and its thermal stabilization. Different circuits has been presented on the basis of the circuits which appearing in examinations. The focus on topics which are important for different competitive examinations. It is an important topic for GATE, ESE and PSU examinations. There are frequent questions from this topic in competitive examinations of Electronics, Electrical and Instrumentation Engineering students.

#### Chapter 3

Chapter 3 presents different biasing circuits of MOSFETs and JFETs. This topic is important for students of Electronics Engineering special for GATE examination. Various circuits of MOSFET have been covered on the basis of questions which appeared in different competitive examinations.

#### Chapter 4

Chapter 4 presents the small signal analysis of BJT amplifiers. This an important topic for GATE as well as ESE mains examinations of students from Electronics and Electrical Engineering. There are frequent questions in GATE of Instrumentation Engineering as well, form this topic.

#### Chapter 5

Chapter 5 presents the small signal analysis of MOSFET amplifiers. This an important topic for GATE specially for students of Electronics Engineering. There topic will be important for future GATE examinations because of increased practical applications of MOSFET.

#### Chapter 6

Chapter 6 presents frequency response of BJT and MOFETs. It covers both low frequency as well

as high frequency responses of these devices. This is an important topic for GATE examinations of Electronics Engineering and ESE pre examination.

### Chapter 7

Chapter 7 presents multistage amplifiers and their frequency response. There were few questions from frequency response of multistage amplifiers in GATE as well as ESE pre in Electronics Engineering. However, there can be one mark question in GATE, ESE pre and PSU examinations from this topic.

### Chapter 8

Chapter 8 presents compound configurations of BJT and MOSFET which includes Darlington Pari, Cascase and Cascode connection and current mirrors. There are frequent question especially from current mirror in GATE examination of Electronics, Electrical and Instrumentation Engineering. It is an important topic of ESE and IAS examinations also.

### **CHAPTERWISE GATE SYLLABUS**

| S.N. | Торіс                                     | Electronics & Comm.<br>Engineering                                                                                                                                                                                                                                                                                                 | Electrical<br>Engineering                                   | Instrumentation<br>Engineering                               |  |  |  |  |  |

|------|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|--------------------------------------------------------------|--|--|--|--|--|

| Ch.1 | Semiconductors                            | Energy bands in intrinsic and<br>extrinsic semiconductors,<br>equilibrium carrier<br>concentration, direct<br>and indirect band-gap<br>semiconductors, Carrier<br>transport: diffusion current,<br>drift current, mobility and<br>resistivity, generation and<br>recombination of carriers,<br>Poisson and continuity<br>equations |                                                             |                                                              |  |  |  |  |  |

| Ch.2 | Diodes                                    | P-N junction, Zener diode,<br>LED, photo diode and solar<br>cell                                                                                                                                                                                                                                                                   |                                                             | Characteristics and<br>applications of diode,<br>Zener diode |  |  |  |  |  |

| Ch.3 | Bipolar Junction<br>Transistors           | BJT                                                                                                                                                                                                                                                                                                                                |                                                             | Characteristics and applications of BJT                      |  |  |  |  |  |

| Ch.4 | Field Effect<br>Transistors               | MOSFET & MOS Capacitor                                                                                                                                                                                                                                                                                                             |                                                             | Characteristics<br>and applications of<br>MOSFET             |  |  |  |  |  |

| Ch.5 | Diodes Circuits                           | Diode circuits: clipping, clamping and rectifiers.                                                                                                                                                                                                                                                                                 | Simple diode<br>circuits: clipping,<br>clamping, rectifiers |                                                              |  |  |  |  |  |

| Ch.6 | BJT Biasing<br>& Thermal<br>Stabilization | BJT amplifiers: biasing                                                                                                                                                                                                                                                                                                            | Amplifiers: Biasing                                         |                                                              |  |  |  |  |  |

| Ch.7 | MOSFET<br>Biasing                         | MOSFET amplifiers: biasing                                                                                                                                                                                                                                                                                                         | Amplifiers: Biasing                                         |                                                              |  |  |  |  |  |

| Ch.8 | Small Signal<br>Analysis of BJT           | BJT amplifiers: ac<br>coupling, small signal<br>analysis                                                                                                                                                                                                                                                                           | Amplifiers:<br>Equivalent circuit                           | small signal analysis of<br>transistor circuits              |  |  |  |  |  |

| Ch.9 | Small Signal<br>Analysis of FET           | MOSFET amplifiers: ac<br>coupling, small signal<br>analysis                                                                                                                                                                                                                                                                        | Amplifiers:<br>Equivalent circuit                           | small signal analysis of<br>transistor circuits              |  |  |  |  |  |

| Chap. | Торіс                                       | Electronics & Comm.                                                                                                               | Electrical                                                                                                                                           | Instrumentation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       |                                             | Engineering                                                                                                                       | Engineering                                                                                                                                          | Engineering                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Ch10  | Frequency                                   | BJT and MOSFET amplifiers                                                                                                         | Amplifiers:                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|       | Response                                    | : frequency response                                                                                                              | Frequency response                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Ch.11 | Multistage<br>Amplifiers                    |                                                                                                                                   |                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Ch.12 | Compound<br>circuits                        | BJT and MOSFET amplifiers<br>: Current mirror                                                                                     |                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Ch.13 | Feedback<br>Amplifiers                      |                                                                                                                                   | Feedback amplifiers                                                                                                                                  | Feedback amplifiers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Ch.14 | Differential<br>Amplifiers                  | BJT and MOSFET amplifiers : differential amplifiers.                                                                              | BJT and MOSFET<br>Differential<br>Amplifiers                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Ch.15 | Operational<br>Amplifiers & its<br>circuits | Op-amp circuits: Amplifiers,<br>summers, differentiators,<br>integrators, active filters,<br>Schmitt triggers and<br>oscillators. | operational<br>amplifiers:<br>characteristics<br>and applications;<br>single stage active<br>filters, Sallen Key,<br>Butterworth, VCOs<br>and timers | Characteristics of<br>ideal and practical<br>operational amplifiers;<br>applications of opamps:<br>adder, subtracter,<br>integrator, differentiator,<br>difference amplifier,<br>instrumentation<br>amplifier, precision<br>rectifier, active filters,<br>oscillators, signal<br>generators, voltage<br>controlled oscillators<br>and phase locked loop,<br>sources and effects of<br>noise and interference<br>in electronic circuited<br>oscillators, signal generators,<br>voltage controlled<br>oscillators,<br>signal generators,<br>voltage controlled<br>oscillators and phase<br>locked loop. |

| Ch.16 | Oscillators                                 |                                                                                                                                   | Oscillators                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Ch.17 | Power Supplies                              |                                                                                                                                   |                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Ch.18 | Power<br>Amplifiers                         |                                                                                                                                   |                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

### **CHAPTERWISE ANALYSIS OF GATE QUESTIONS**

| Electronics and Communication Engineering : EDC & Analog Electronic |                                       |      |      |      |      |    | lics | •  |    |    |      |    |    |      |    |    |    |      |      |      |      |

|---------------------------------------------------------------------|---------------------------------------|------|------|------|------|----|------|----|----|----|------|----|----|------|----|----|----|------|------|------|------|

| Chap                                                                | Торіс                                 | 2010 | 2011 | 2012 | 2013 |    | -    | 14 |    |    | 2015 |    |    | 2016 |    |    | 17 | 2018 | 2019 | 2020 | 2021 |

|                                                                     | •                                     |      |      |      |      | IV |      | -  | 1  | ш  | -    | 1  |    | =    | -  | -  | -  |      |      |      |      |

| Ch.1                                                                | Semiconductors                        | 4    | 1    |      |      | 7  | 2    | 3  |    |    | 6    | 1  |    | 2    | 5  |    | 5  |      |      | 1    | 2    |

| Ch.2                                                                | Diodes                                | 2    | 2    |      | 1    |    | 3    |    | 4  |    |      | 5  | 4  | 4    | 2  | 4  | 3  | 12   | 10   | 5    | 2    |

| Ch.3                                                                | BJT and Its Characteristics           | 2    | 2    |      |      | 2  |      | 1  | 2  | 3  |      |    | 2  | 1    |    | 1  | 1  |      | 1    | 2    |      |

| Ch.4                                                                | FET and Its Characteristics           | 2    | 6    | 8    | 5    |    | 7    | 5  | 4  | 5  | 2    | 4  | 3  | 5    | 4  | 8  | 2  | 3    | 3    | 2    | 2    |

| Ch.5                                                                | Diode circuits                        |      | 4    | 3    | 4    | 1  |      | 2  | 1  | 3  | 3    | 1  | 3  | 2    |    | 1  |    |      | 5    | 1    | 2    |

| Ch.6                                                                | Biasing of BJT                        |      | 2    |      | 2    |    | 3    | 1  |    | 1  |      |    | 1  |      |    | 1  | 2  |      |      |      |      |

| Ch.7                                                                | Biasing of MOSFET                     |      |      |      |      |    |      |    |    |    |      |    |    |      |    |    |    |      |      | 2    | 2    |

| Ch.8                                                                | Small Signal Analysis of BJT          | 2    |      | 1    |      | 7  |      |    | 2  |    | 2    |    | 4  |      |    | 2  | 2  |      |      | 2    |      |

| Ch.9                                                                | Small Signal Analysis of FET          | 2    |      | 1    |      | 7  |      |    | 2  |    | 2    |    | 4  |      |    | 2  | 2  |      |      | 2    | 1    |

| Ch.10                                                               | Frequency Response                    | 4    |      |      |      |    |      |    |    |    |      |    |    |      |    |    | 1  |      |      |      |      |

| Ch.11                                                               | Multistage Amplifiers                 |      |      |      |      |    |      | 1  |    |    |      |    |    | 1    |    |    |    |      |      |      |      |

| Ch.12                                                               | Compoud circuits                      | 1    |      |      |      |    |      |    |    |    |      |    |    | 1    |    |    |    |      | 4    |      |      |

| Ch.13                                                               | Feedback Amplifiers                   |      |      | 2    | 1    |    | 1    | 1  | 1  |    |      |    |    |      |    |    | 1  | 1    |      |      |      |

| Ch.14                                                               | Differential Amplifiers               |      |      |      |      |    |      | 1  |    |    |      | 2  |    |      |    |    |    |      |      |      |      |

| Ch.15                                                               | Operational Amplifiers & its circuits | 3    | 1    | 2    | 3    | 2  | 2    |    | 6  | 3  | 6    | 4  | 3  | 4    | 8  | 2  | 3  | 4    |      | 4    | 4    |

| Ch.16                                                               | Oscillators                           |      |      |      |      |    |      |    |    |    |      |    |    |      |    |    |    |      |      |      |      |

| Ch.17                                                               | Power Supplies                        |      |      |      |      |    |      |    |    |    |      |    |    |      |    |    |    |      |      | 2    |      |

| Ch.18                                                               | Power Amplifiers                      |      |      |      |      |    |      |    |    |    |      |    |    |      |    |    |    |      |      |      |      |

|                                                                     | Total Marks                           | 22   | 18   | 14   | 16   | 26 | 18   | 19 | 22 | 15 | 21   | 17 | 24 | 20   | 19 | 21 | 22 | 20   | 23   | 23   | 15   |

| Electrical End  | aineerina | : EDC & Anal | og Eectronics |

|-----------------|-----------|--------------|---------------|

| Electrical Elig | Juicering |              |               |

|           |                                       |      | _    |      |      |           |   |   |                  |   |   |                  |  |   |        |    |      |      |      |      |   |

|-----------|---------------------------------------|------|------|------|------|-----------|---|---|------------------|---|---|------------------|--|---|--------|----|------|------|------|------|---|

| Chap      | Торіс                                 | 2010 | 2011 | 2012 | 2013 | 2013 2014 |   |   | 2015<br>III II I |   |   | 2016<br>III II I |  |   | 20<br> | 17 | 2018 | 2019 | 2020 | 2021 |   |

| -<br>Ch.1 | Semiconductors                        |      |      |      |      | IV        |   |   | -                |   |   |                  |  |   |        |    | •    |      |      |      |   |

| Ch.2      | Diodes                                |      |      |      |      |           |   |   |                  |   |   |                  |  |   |        |    |      |      |      | 2    |   |

| Ch.3      | BJT and Its Characteristics           |      |      |      |      |           |   |   |                  |   | 1 |                  |  |   |        |    |      |      |      | 1    |   |

| Ch.4      | FET and Its Characteristics           |      |      |      |      |           |   |   |                  |   |   |                  |  |   |        |    |      |      | 1    | 2    |   |

| Ch.5      | Diode circuits                        |      | 2    | 2    | 4    |           |   | 2 |                  |   | 2 |                  |  |   | 3      |    |      |      |      |      | 4 |

| Ch.6      | BJT Biasing                           |      | 2    | 2    |      |           |   |   |                  |   | 1 | 1                |  |   | 1      | 2  |      | 2    | 2    | 2    | 1 |

| Ch.7      | FET Biasing                           |      |      |      |      |           |   |   |                  |   |   |                  |  |   |        |    |      |      |      |      |   |

| Ch.8      | Small Signal Analysis of BJT          |      |      |      |      |           |   |   |                  | 1 |   |                  |  |   |        |    |      |      |      | 1    |   |

| Ch.9      | Small Signal Analysis of FET          |      |      |      |      |           |   |   |                  |   |   |                  |  |   |        |    |      |      |      |      |   |

| Ch.10     | Frequency Response of BJT & MOSFET    |      |      |      |      |           |   |   |                  |   |   |                  |  |   |        |    |      |      |      |      |   |

| Ch.11     | Multistage Amplifiers                 |      |      |      |      |           |   |   |                  |   |   |                  |  |   |        |    |      |      |      |      |   |

| Ch.12     | Compoud circuits                      |      |      |      |      |           |   |   |                  |   |   |                  |  |   |        |    |      |      |      |      |   |

| Ch.13     | Feedback Amplifiers                   |      |      | 2    | 1    |           |   |   |                  |   |   |                  |  |   |        |    |      |      | 1    |      |   |

| Ch.14     | Differential Amplifiers               |      |      |      |      |           |   |   |                  |   |   |                  |  |   |        |    | 2    |      |      | 2    |   |

| Ch.15     | Operational Amplifiers & its circuits | 1    | 1    | 4    | 3    |           | 3 | 2 | 3                |   | 4 | 4                |  | 3 |        | 2  | 2    |      | 2    |      | 2 |

| Ch.16     | Oscillators                           |      |      |      |      |           |   |   |                  |   |   |                  |  |   |        |    |      |      |      |      |   |

| Ch.17     | Power Supplies                        |      |      |      |      |           |   |   |                  |   |   |                  |  |   |        |    |      |      |      | 2    |   |

| Ch.18     | Power Amplifiers                      |      |      |      |      |           |   |   |                  |   |   |                  |  |   |        |    |      |      |      |      |   |

|           | Total Marks                           | 1    | 5    | 10   | 8    |           | 3 | 4 | 5                | 1 | 8 | 5                |  | 3 | 4      | 4  | 4    | 2    | 6    | 12   | 7 |

| Instrumentation Engineering : EDC & Analog Eectronics |                                    |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

|-------------------------------------------------------|------------------------------------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|

| Chap                                                  | Торіс                              | 2010 | 2011 | 2012 | 2013 | 2014 | 2015 | 2016 | 2017 | 2018 | 2019 | 2020 | 2021 | 2022 | 2023 | 2024 |

| Ch.1                                                  | Semiconductors                     |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| Ch.2                                                  | Diodes and theirs circuits         |      |      |      |      |      |      | 3    | 2    |      | 1    |      |      |      |      |      |

| Ch.3                                                  | BJT & Its Characteristics          |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| Ch.4                                                  | FET Characteristics and its biasin |      |      |      |      |      | 2    |      | 2    |      |      |      |      |      |      |      |

| Ch.5                                                  | Diodes Circuits                    |      | 2    | 2    | 4    | 1    | 1    |      | 1    | 1    | 1    | 3    |      |      |      |      |

| Ch.6                                                  | BJT Biasing                        |      |      |      | 1    | 4    | 2    |      |      |      |      |      |      |      |      |      |

| Ch.7                                                  | FET Biasing                        |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| Ch.8                                                  | Small Signal Analysis of BJT       |      | 1    |      | 1    |      | 2    |      |      |      | 2    |      |      |      |      |      |

| Ch.9                                                  | Small Signal Analysis of FET       |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| Ch.10                                                 | Frequency Response of BJT & MOSFET |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| Ch.11                                                 | Multistage Amplifiers              |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| Ch.12                                                 | Compound circuits                  | 2    |      |      |      |      |      |      |      |      | 2    |      | 3    |      |      |      |

| Ch.13                                                 | Feedback Amplifiers                |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| Ch.14                                                 | Differential Amplifiers            |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| Ch.15                                                 | Operational Amplifiers             | 7    | 11   | 2    | 12   | 8    | 4    | 15   | 8    | 7    | 3    |      | 5    |      |      |      |

| Ch.16                                                 | Oscillators                        |      |      |      |      |      |      |      | 1    |      |      | 9    |      |      |      |      |

| Ch.17                                                 | Power Supplies                     |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| Ch.18                                                 | Power Amplifiers                   |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| Ch.19                                                 | Tuned Amplifiers                   |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| Ch.20                                                 | Multivibrators                     |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

|                                                       | Total Marks                        | 9    | 14   | 4    | 18   | 13   | 11   | 18   | 14   | 8    | 9    | 12   | 8    |      |      |      |

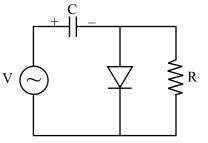

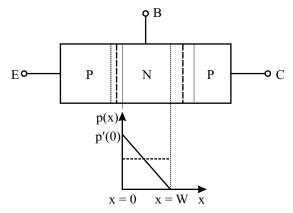

#### 1.1 **Diode as Circuit Element**

When a diode is used as a circuit component it behaves like an uncontrolled switch. Ideally a diode behaves like a closed switch when it is forward biased and it behaves like an open switch when it is reverse biased. However, a diode may be represented by its equivalent circuit with different diode models.

#### 1.1.1 Equivalent Circuit of an Diode for DC signals

The diodes are replaced by their equivalent circuit in diode circuits depending upon the biasing condition of the diode. The diodes equivalent circuit for different diode models are presented as under.

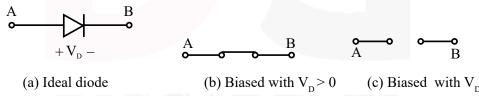

#### 1. Ideal Diode

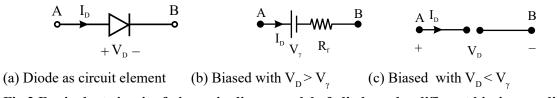

An ideal diode behaves as short circuit when it is forward biased with  $V_p > 0$  and open circuit when it is reverse biased with  $V_p < 0$  as shown in Fig. 1

(b) Biased with  $V_p > 0$  (c) Biased with  $V_p < 0$

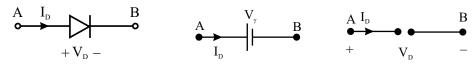

#### 2. Piecewise Linear Model

The piecewise linear model represents a battery in series with a resistance  $(R_{e})$  called forward resistance, when voltage across the diode is more than cut-in voltage  $(V_y)$  of the diode and it acts as an open circuit when voltage across the diode is less than cut in voltage of the diode as shown below.

Fig.2 Equivalent circuit of piece wise linear model of diode under different biasing conditions

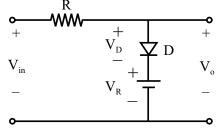

#### 3. Simplified Model

A diode in simplified model is represented by a battery when voltage across the diode is more than the cut-in voltage  $(V_{\gamma})$  of the diode and it acts as an open circuit when voltage across the diode is less than cut in voltage as shown below.

(a) Diode as circuit element (b) Biased with  $V_D > V_\gamma$  (c) Biased with  $V_D < V_\gamma$ Fig.3 Equivalent circuit of simplified model of diode under different biasing conditions

#### **1.2 Clipping Circuits**

Clipping circuits are used for clipping a part of a waveform which lies above or below a reference voltage level. The clipping circuits can be used to clip waveforms at one or two reference levels. The clipping circuit which clips a waveform at one reference level is called one level clipper and one which clips at two reference levels is called two level clipper. The clipper which clips the waveform above a reference level is called positive level clipper and one which clips below a reference level is called a negative level clipper. While studying the clipping circuits only two cases will be discussed with diode in 'ON' condition and diode in 'OFF' condition. The diode will be considered 'ON' when voltage across the diode,  $V_D > V_{\gamma}$ , and it is considered 'OFF' when  $V_D < V_{\gamma}$ . The cut-in voltage,  $V_{\gamma} = 0$ , for an ideal diode. The diodes used in clipping circuits in the following sections will be considered ideal diodes and input signals are considered to be sinusoidally time varying.

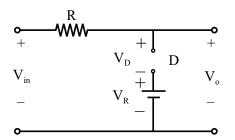

#### 1.2.1 One Level Clipper with Shunt Connected Diode

These are the circuits in which diode is connected in shunt with the load. The reference voltage source is connected in series with diode and this combination is connected in shunt with the load. One level clippers can be positive and negative level clippers which are further subdivided in to two sub category each with positive and negative reference voltages. All possible one level clippers with shunt connected diode are discussed as follows,

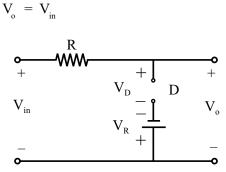

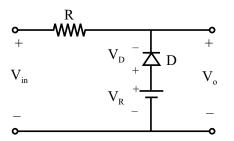

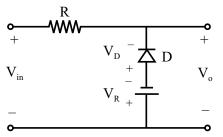

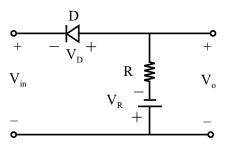

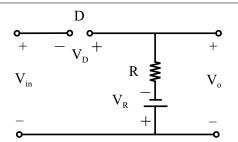

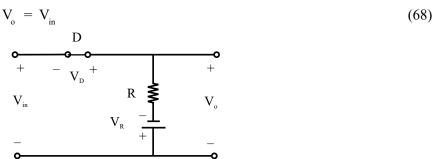

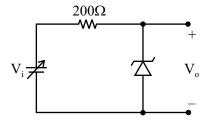

#### Circuit 1: Positive Level Clipper Circuits with Positive Reference

A positive level clipper with positive reference voltage consisting of a shunt branch with a reference voltage source in series with an ideal diode connected across the load is shown in Fig.4. The reference voltage is positive if its polarity matches with polarity of input voltage. It can be seen from the circuit of Fig. 4 that negative terminal of reference voltage source is common with negative terminal of input voltage so the reference voltage is called positive reference. The analysis of clipping circuits will be done by taking OFF condition of diode followed by ON condition for ease of understanding the operation of the circuit which is discussed in the following two cases.

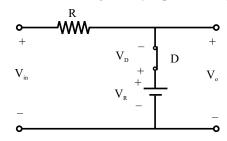

#### Case-1 : When diode D is OFF

The equivalent circuit with diode D in OFF condition becomes as shown in Fig. 5. As the diode D is ideal so it behaves like an open circuit when it is OFF. The diode D is off when voltage across the diode negative i.e.  $V_D < 0$ . If a KVL is applied in input loop of the circuit as shown below with diode in open circuited condition then the voltages,  $V_{in}$ ,  $V_D$  and  $V_R$  are related as under,

*:*..

$$in - V_{\rm D} - V_{\rm R} = 0$$

V

(1)

One point should be noted here that the voltage drop across the resistance R is not considered while applying KVL in input loop because the current in R is zero when diode is open circuited, therefore, voltage drop across R is zero.

Fig.4 Shunt diode positive level clipper circuit with positive reference voltage

$$\Rightarrow \qquad V_{\rm p} = V_{\rm in} - V_{\rm R} \tag{2}$$

The diode D is off if,

$$V_{\rm D} < 0$$

(3)

$$\Rightarrow \qquad V_{in} - V_R < 0 \tag{4}$$

$$\Rightarrow \qquad V_{in} < V_P \tag{5}$$

Under open circuited condition of the diode, the current through resistance R is zero, so voltage drop across R is zero and the output voltage becomes same as input voltage.

$$V_{o} = V_{in}$$

(6)

Fig.5 Equivalent circuit of positive level clipper circuit with positive reference voltage and  $V_p < 0$

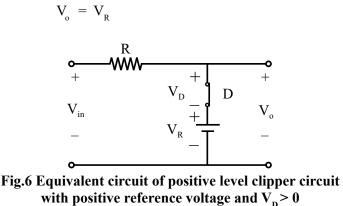

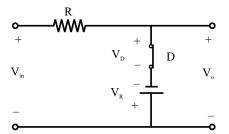

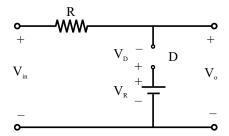

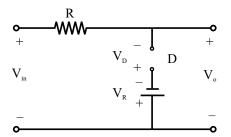

#### Case-2: When diode D is ON

The equivalent circuit with diode D in ON condition becomes as shown in Fig. 6. As the diode D is ideal so it behaves like a short circuit when it is ON. When diode is in OFF condition the voltage across the diode is given by equation (2). The diode will turn ON from OFF only at the instant when  $V_{\rm p}$  becomes more than zero.

The diode D turns on ON when,

$$V_{\rm p} > 0 \tag{7}$$

$$V_{in} - V_R > 0 \tag{8}$$

$$\Rightarrow$$

$\Rightarrow$

Under short circuited condition of the diode, the battery with reference voltage V<sub>R</sub> is directly

$V_{in} > V_{p}$

(9)

(10)

connected across the output terminals so the output voltage becomes equal to  $V_R$ . Thus when the input voltage is greater  $V_R$ , the output voltage,

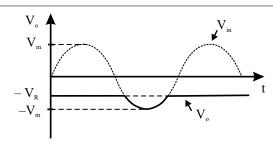

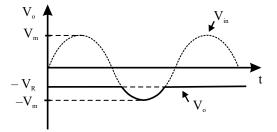

#### Waveforms:

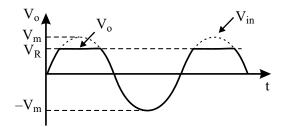

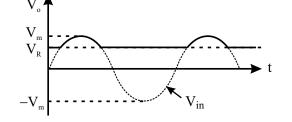

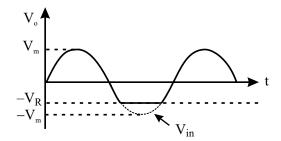

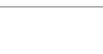

If input signal is sinusoidal then waveform of output and input signals will be as shown in Fig.7. The sinusoidal waveform with dotted line represents the input signal and part of sinusoidal waveform with dark line represents the output signal. It can be observed from the waveform that when input signal is less the reference voltage  $V_R$  the output signal is same as input signal and when input signal becomes more than the reference voltage level the output signal is clipped at reference voltage  $V_R$ .

Fig.7 Waveform of input and output signals of positive level clipper circuit with positive reference voltage

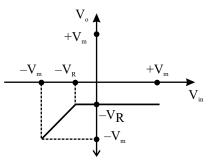

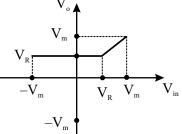

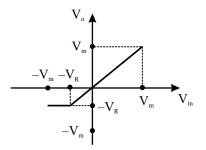

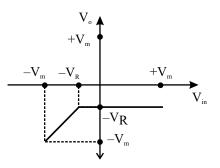

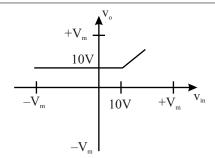

#### **Transfer characteristics:**

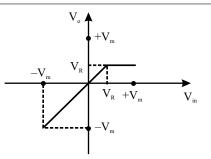

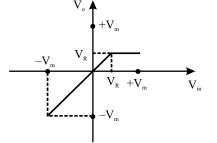

The transfer characteristics of clipper circuit gives the variation of output voltage with respect to input voltage. It observed from the waveforms of input and output signals in Fig.7 that the input voltage varies from  $-V_m$  to  $+V_m$  and corresponding variation in output voltage of the circuit is from  $-V_m$  to  $+V_R$ . Fig. 8 represents the transfer characteristics of the of a positive level clipper circuit with positive reference voltage.

When

$$V_{in} \leq V_{R}$$

;  $V_{o} = V_{in}$  (11)

If y-axis of transfer characteristics represents output voltage and x-axis represents input voltage then above equation represents a straight line of unit slope for the range  $V_{in} \le V_R$  as shown in Fig. 8. When  $V_{in} \ge V_R$ ;  $V_a = V_R$  (12)

So, the output voltage is  $V_{R}$  when the input voltage becomes more than  $V_{R}$  as shown in the Fig. 8.

Fig.8 Transfer characteristics of positive level clipper circuit with positive reference voltage

**Note**: When  $V_p$  is zero the above circuit behaves like a half wave rectifier, with only negative half cycle presents at the output.

#### Circuit 2: **Positive Level Clipper with Negative Reference**

A positive level clipper with negative reference voltage consisting of a shunt branch with a reference voltage source in series with an ideal diode connected across the load is shown in Fig.9. The reference voltage is negative if its polarity is opposite to that of input voltage as in circuit of Fig. 9.

Fig.9 Shunt diode positive level clipper circuit with negative reference voltage

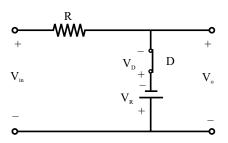

#### Case-1: When diode D is OFF

The equivalent circuit with diode D in OFF condition becomes as shown in Fig. 10. The diode D is off when voltage across the diode negative i.e.  $V_{D} < 0$ . If a KVL is applied in input loop of the circuit as shown below with diode in open circuited condition then the voltages,  $V_{in}$ ,  $V_{D}$  and  $V_{R}$  are related as under,

$$V_{in} - V_D + V_R = 0$$

(13)

The voltage drop across the resistance R is not considered while applying KVL in input loop because the current in R is zero when diode is open circuited. Therefore, voltage drop across R is zero.

$$\Rightarrow$$

$$V_{\rm p} = V_{\rm in} + V_{\rm p} \tag{14}$$

The diode D is off if,

$$V_{r} < 0$$

(15)

$$\Rightarrow V_{ip} + V_{p} < 0$$

$$\Rightarrow$$

$V_{R} < 0$  $V_{in} < -V_{R}$ (17)

Under open circuited condition of the diode, the current through resistance R is zero, so voltage drop across R is zero and the output voltage becomes same as input voltage.

(16)

*.*..

(20)

Fig.10 Equivalent circuit of positive level clipper circuit with negative reference voltage and  $V_p < 0$

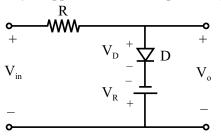

#### Case-2: When diode D is ON

The equivalent circuit with diode D in ON condition becomes as shown in Fig.11. When diode is in OFF condition the voltage across the diode is given by equation (14). The diode will turn ON from OFF only at the instant when  $V_{D}$  becomes more than zero.

The diode D turns on ON when,

V + V > 0

$$V_{\rm p} > 0 \tag{19}$$

$$\Rightarrow$$

$$V > V$$

(21)

$$\Rightarrow$$

*.*..

$V_{in} > - V_R$ (21)Under short circuited condition of the diode, the battery is directly connected across the output terminals. However, the polarity of output voltage and that of battery is opposite so the output voltage is equal to  $-V_{p}$ . Thus when the input voltage is greater than  $-V_{p}$  the output voltage,

> $V_{R} = -V_{R}$ (22)

Fig.11 Equivalent circuit of positive level clipper circuit with negative reference voltage and  $V_p > 0$

#### Waveforms:

The waveforms of output signal for a sinusoidal input signal is shown in Fig.12. The sinusoidal waveform with dotted line represents the input signal and part of sinusoidal waveform with dark line represents the output signal. It can be observed from the waveform that when input signal is less the reference voltage,  $-V_{\rm p}$ , the output signal is same as input signal and when input signal becomes more than the reference voltage level the output signal is clipped at reference voltage  $-V_{R}$ .

Fig.12 Waveform of input and output signals of positive level clipper with negative reference voltage

#### **Transfer characteristics:**

It observed from the waveforms of input and output signals in Fig.12 that the input voltage varies from  $-V_m$  to  $+V_m$  and corresponding variation in output voltage of the circuit is from  $-V_m$  to  $-V_m$ . Fig. 13 represents the transfer characteristics of the of a positive level clipper circuit with negative reference voltage.

When

$$V_{in} \leq -V_R$$

;  $V_o = V_{in}$  (23)

Above equation represents a straight ling of unit slope.

When

$$V_{in} \ge -V_R$$

;  $V_o = -V_R$  (24)

#### Fig.13 Transfer characteristics of positive level clipper circuit with negative reference voltage

#### Circuit 3: Negative Level Clipper with Positive Reference

A negative level clipper with positive reference voltage consisting of a shunt branch with a reference voltage source in series with an ideal diode connected across the load is shown in Fig.14.

Fig.14 Shunt diode negative level clipper circuit with positive reference voltage

#### Case-1 : When diode D is OFF

The equivalent circuit with diode D in OFF condition becomes as shown in Fig. 15. The KVL on

$\Rightarrow$

$\Rightarrow$

$\Rightarrow$

input side of the circuit gives,

$$V_{in} - V_{R} + V_{D} = 0$$

(25)

The voltage drop across R is zero because the diode is open.

$$V_{\rm D} = -V_{\rm in} + V_{\rm R} \tag{26}$$

The diode D is off if,

$$V_{\rm p} < 0$$

(27)

$$-V_{in} + V_R < 0 \tag{28}$$

$$V_{in} > V_{p} \tag{29}$$

Under open circuited condition of the diode, the current through resistance R is zero, so voltage drop across R is zero and the output voltage becomes same as input voltage.

Fig.15 Equivalent circuit of negative level clipper circuit with positive reference voltage and  $V_p < 0$

#### Case-2: When diode D is ON

The equivalent circuit with diode D in ON condition becomes as shown in Fig.16. When diode is in OFF condition the voltage across the diode is given by equation (26).

Fig.16 Equivalent circuit of negative level clipper with positive reference voltage and  $V_p > 0$

The diode D turns on ON when,

$-V_{in} + V_R > 0$

$$V_{\rm D} > 0 \tag{31}$$

$$\Rightarrow$$

www.digcademy.com

digcademy@gmail.com

(32)

Under short circuited condition of the diode, the battery is directly connected across the output terminals. Then the output voltage,

$$\therefore \qquad \qquad V_{o} = V_{R} \qquad (34)$$

#### Waveforms:

The waveforms of output signal for a sinusoidal input signal is shown in Fig.17. It can be observed from the waveform that when input signal is less the reference voltage,  $V_R$ , the output signal is clipped at voltage level  $V_R$  and when input signal becomes more than the reference voltage, the output signal is same as input voltage.

Fig.17 Waveform of input and output signals of negative level clipper with positive reference voltage

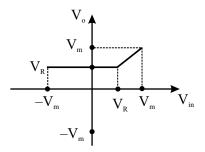

#### **Transfer characteristics:**

It is seen from above waveform that the output voltage varies from  $+ V_R$  to  $+V_m$  for corresponding change of input voltage from  $-V_m$  to  $+V_m$ . Fig. 18 represents the transfer characteristics of the of a negative level clipper circuit with positive reference voltage.

When

$$V_{in} \leq V_{p}$$

;  $V_{a} = V_{p}$  (35)

When

$$V_{in} \ge V_{P}$$

;  $V_{a} = V_{in}$  (36)

Thus the output clipped at level  $V_R$  for  $V_{in} \le V_R$  and it is a straight line of unity slope for the range  $V_{in} \ge V_R$  as shown in Fig. 18.

#### Fig.18 Transfer characteristics of negative level clipper with positive reference

#### Circuit 4: Negative Level Clipper with Negative Reference

A negative level clipper with negative reference voltage consisting of a shunt branch with a reference

www.digcademy.com

$\Rightarrow$

*:*..

voltage source in series with an ideal diode connected across the load is shown in Fig.19.

Fig.19 Shunt diode negative level clipper with negative reference voltage

#### Case-1 : When diode D is OFF

The equivalent circuit with diode D in OFF condition becomes as shown in Fig. 20. The KVL on input side of the circuit gives,

$$V_{in} + V_D + V_R = 0 \tag{37}$$

The voltage drop across R is zero because the diode is open.

$$V_{\rm D} = -V_{\rm in} - V_{\rm R} \tag{38}$$

The diode D is off if,

$$V_{\rm p} < 0$$

(39)

$$\Rightarrow \qquad -V_{\rm in} - V_{\rm p} < 0 \tag{40}$$

$$\Rightarrow \qquad V_{in} > -V_{P} \tag{41}$$

Under open circuited condition of the diode, the current through resistance R is zero, so voltage drop across R is zero and the output voltage becomes same as input voltage.

$V_{o} = V_{in}$ (42)

Fig.20 Equivalent circuit of negative level clipper with negative reference voltage and  $V_p < 0$

#### Case-2: When diode D is ON

The equivalent circuit with diode D in ON condition becomes as shown in Fig. 21. When diode is in OFF condition the voltage across the diode is given by equation (38).

The diode D turns on ON when,

$$V_{\rm D} > 0 \tag{43}$$

$$\Rightarrow$$

$-V_{in} - V_{R} > 0 \tag{44}$

$\Rightarrow$

V<sub>in</sub>

r

$$< -V_{R}$$

(45)

Under short circuited condition of the diode, the battery is directly connected across the output terminals. Then the output voltage,

$$V_{o} = -V_{R}$$

(46)

#### Waveforms:

The waveforms of output signal for a sinusoidal input signal is shown in Fig.22. It can be observed from the waveform that when input signal is less the reference voltage,  $-V_R$ , the output signal is clipped at voltage level  $-V_R$  and when input signal becomes more than the reference voltage, the output signal is same as input voltage.

Fig.22 Waveform of input and output signals of negative level clipper with negative reference voltage

#### **Transfer characteristics:**

It is seen from above waveform that the output voltage varies from  $-V_R$  to  $+V_m$  for corresponding change of input voltage from  $-V_m$  to  $+V_m$ . Fig. 23 represents the transfer characteristics of the of a negative level clipper circuit with negative reference voltage.

Fig.23 Transfer characteristics of negative level clipper with negative reference

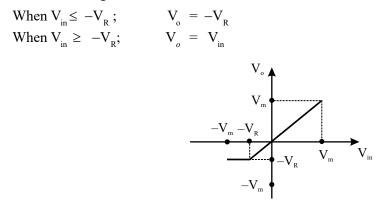

When  $V_{in} \leq -V_R$ ;  $V_o = -V_R$ When  $V_{in} \geq -V_R$ ;  $V_o = V_{in}$ Thus, the output clipped at level  $-V_R$  for  $V_{in} \leq -V_R$  and it is a straight line of unity slope for the range  $V_{in} \geq -V_R$  as shown in Fig. 23.

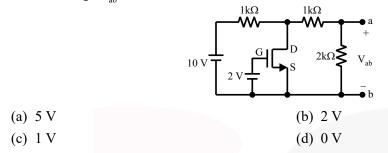

#### Example 1

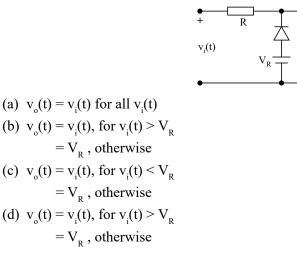

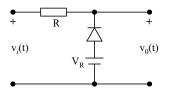

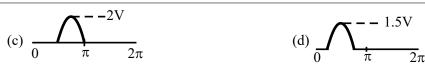

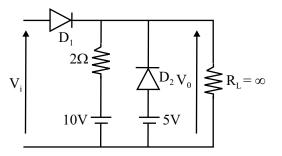

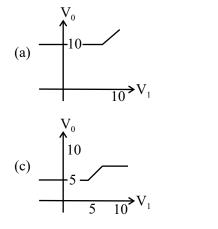

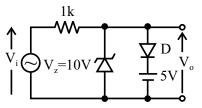

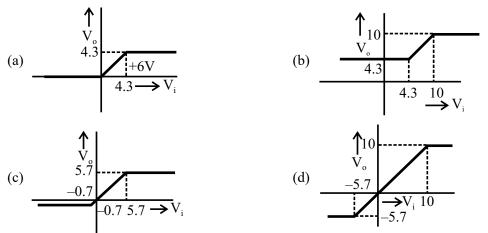

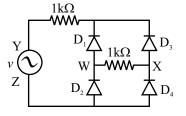

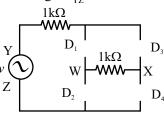

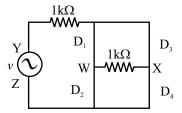

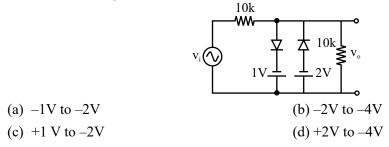

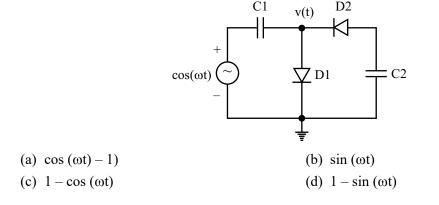

Assuming ideal diode characteristics, the input/output voltage relationship for the circuit shown in figure is

$v_0(t)$

#### Solution : Ans.(d)

The given circuit is clipper circuit with output given by,

Case-I:when $v_i(t) < V_R$ Diode is ON and $v_o(t) = V_R$ Case-II:when $v_i(t) > V_R$ Diode is OFF and  $v_o(t) = v_i(t)$

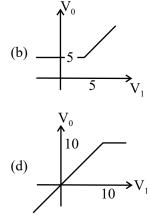

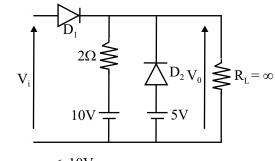

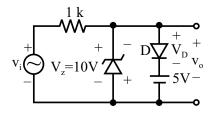

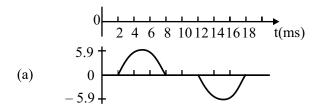

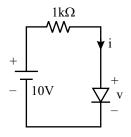

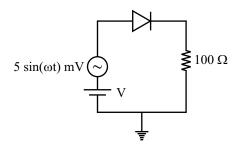

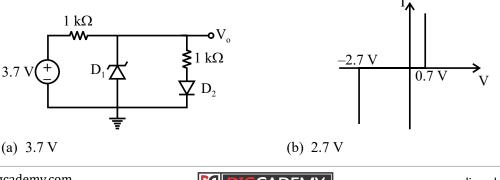

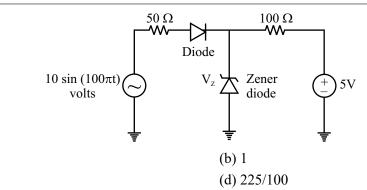

#### Example 2

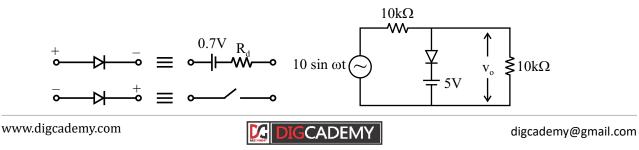

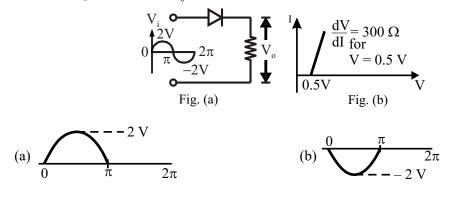

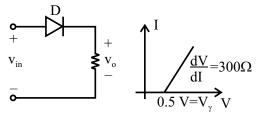

The equivalent circuits of a diode, during forward biased and reverse biased conditions, are shown in the figure.

#### GATE(IN/2004/1M)

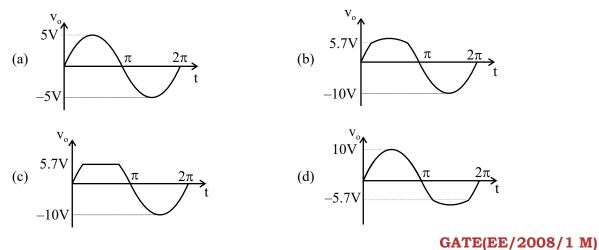

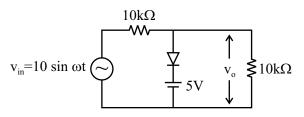

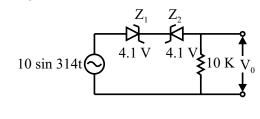

If such a diode is used in clipper circuit of figure given above, the output voltage  $(v_{_{o}})$  of the circuit will be

Solution : Ans.(a)

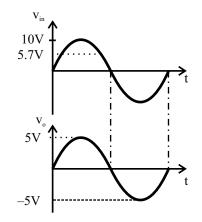

In the circuit shown above the diode will be forward biased only when  $v_{in} > 5.7$  V. The maximum possible value of  $v_o$  in above circuit can reach to  $v_{omax} = \frac{10}{10 \ 10} \times 10$  V = 5V. So, the diode will

remain off all the times and output voltage of circuit will be,

$$\mathbf{v}_{o} = \frac{10}{10+10} \times \mathbf{v}_{in} = 5 \sin \omega t$$

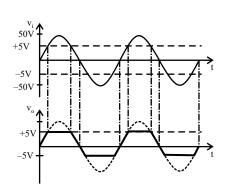

Waveforms :

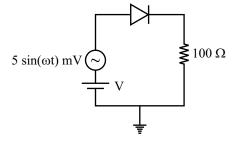

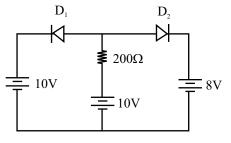

#### Example 3

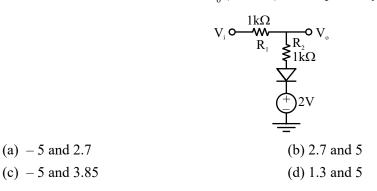

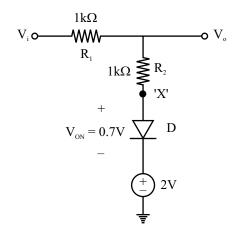

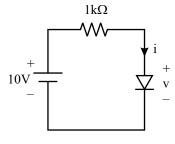

The diode in the circuit shown has  $V_{on} = 0.7$  Volts but is ideal otherwise. If  $V_i = 5sin(\omega t)$  Volts, the

www.digcademy.com

minimum and maximum values of V<sub>o</sub> (in Volts) are, respectively,

**GATE(EC-II/2014/2M)**

#### Solution : Ans. (c)

Given,  $V_i = 5 \sin \omega t$ The diode will OFF when  $V_x < 2.7 V$

Case-I : When  $V_i < 2.7 V$

The diode D is off for  $V_i < 2.7$  V. The equivalent circuit for  $V_i < 2.7$  V becomes as under

÷.

$$V_0 = V_1 = 5 \sin \omega t$$

$V_{o}$  is minimum when sin  $\omega t = -1$

$\therefore$   $V_{o, min} = -5V$

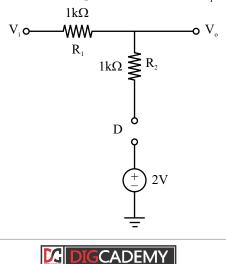

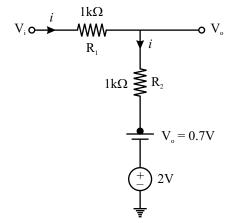

**Case-II**: When  $V_i > 2.7 V$

The diode is turned on when input voltage  $V_i \ge 2.7$  V. The equivalent voltage for  $V_i \ge 2.7$  V will be as under,

Current in resistance R<sub>2</sub>,

$$i = \frac{V_i - 2.7}{R_1 + R_2} = \frac{V_i - 2.7}{2 \, k\Omega}$$

Output voltage

$\therefore \qquad V_{o} = iR_{2} + 2.7 V$   $\Rightarrow \qquad V_{o} = \frac{V_{i} - 2.7}{2k} \times 1k + 2.7$

$$\Rightarrow \qquad V_{o} = \frac{5\sin\omega t}{2} + 1.35$$

$$V_{o} = 2.5 \sin \omega t + 1.35 V$$

Output voltage  $V_0$  is maximum when sin  $\omega t = 1$

$$V_{o, max} = 2.5 + 1.35 = 3.85V$$

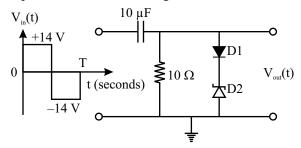

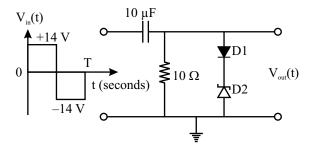

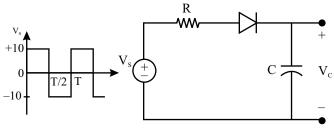

#### 1.2.2 One Level Clipper with Series Connected Diode

These are the circuits with a diode connected in series with load. The reference voltage source is connected in shunt with the load.

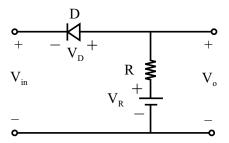

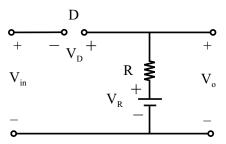

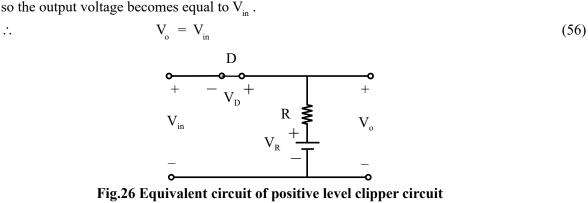

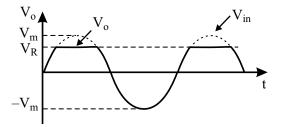

#### Circuit 1: Positive Level Clipper Circuits with Positive Reference

Fig. 24 shows the circuit of one level clipper with series connected diode having positive reference

$\Rightarrow$

*.*..

voltage. Analysis of the circuit will be done by taking OFF condition of diode followed by ON condition for ease of understanding the operation of the circuit which is discussed in the following two cases.

Fig.24 Series diode positive level clipper circuit with positive reference voltage

# Case-1 : When diode D is OFF

The equivalent circuit with diode D in OFF condition becomes as shown in Fig. 25. The diode is assumed to be ideal and it is off when voltage across the diode negative i.e.  $V_D < 0$ . The KVL in input side of the circuit gives,

$$V_{in} + V_D - V_R = 0 \tag{47}$$

Voltage across R is not considered while applying KVL in input loop because the current in R is zero when diode is open.

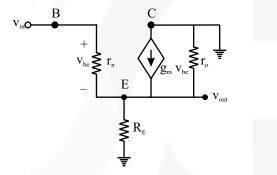

$$\Rightarrow \qquad V_{\rm D} = -V_{\rm in} + V_{\rm R} \tag{48}$$